请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK05318B 工具与软件:

尊敬的 Expert:

我想再次检查 LMK05318B 是否会实现 抖动衰减? 在某个应用场景中、客户的输入和输出时钟信号具有相同的频率和格式、但输入时钟的抖动裕度不足。 我们是否可以期望输出具有更大的抖动裕量?

此致、

海亮

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

嗨、Hailiang、

如果输入时钟的噪声高于 LMK05318B APLL 和 VCO 噪声、则 LMK05318B 会清除抖动。 在大多数应用中、输入噪声更大、因此 LMK05318B 可用作抖动清除器。

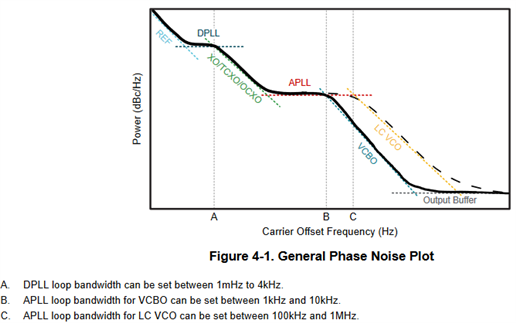

请参阅 SNAA396应用手册中的相位噪声曲线部分(https://www.ti.com/lit/an/snaa396/snaa396.pdf?)。 提供了基准/输入噪声如何影响 PLL (LMK05318B)的输出时钟的解释。 下图显示了 LMK05318B 输出的通用相位噪声图。 您可以看到、DPLL 基准(REF 输入)和 APLL 基准(XO 输入)在低于 APLL 环路带宽(LBW)设置的情况下主导了输出时钟噪声。 除了 APLL LBW、APLL 和 BAW VCO 噪声在相位噪声中占主导地位。 BAW VCO 可在12kHz 至20 MHz 的集成范围内提供出色的抖动性能。

此致、

Jennifer