Other Parts Discussed in Thread: LMX2694EPEVM

工具与软件:

您好!

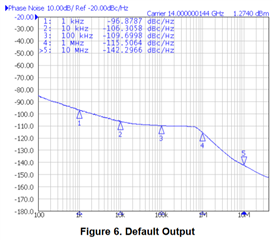

我正在努力重新创建 LMX2694EPEVM 评估说明图6中显示的默认输出、如下所示:

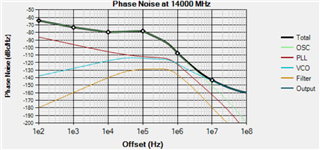

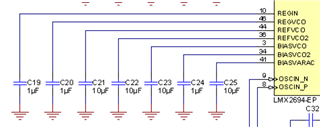

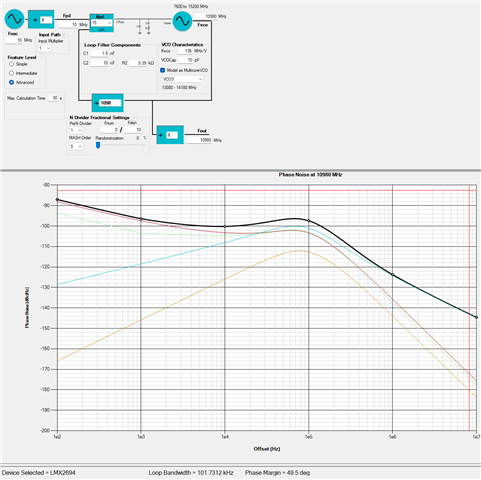

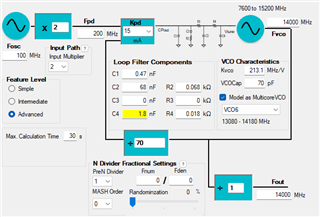

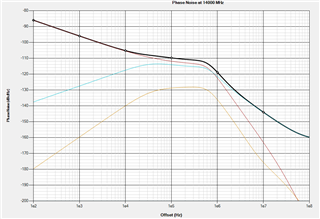

我已使用安装在评估板上的默认环路滤波器对 PLLatinum sim 进行了配置、并验证了仿真的相位噪声是否与评估说明中应该获得的相位噪声相匹配:

我已经按照用户指南图1所示的 EVM 连接图进行了操作、并使用具有适当输入电平的高质量信号发生器来提供此默认配置所需的100 MHz 参考时钟。 我已验证它不应该干扰我的测量、因为该音调的相位噪声明显低于 PLLatinum sim 仿真的整体相位噪声。 它在100Mhz 范围内更高、但我主要关注最高10MHz 的总体相位噪声:

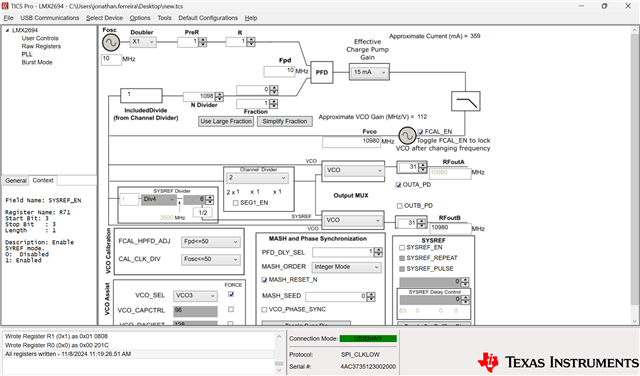

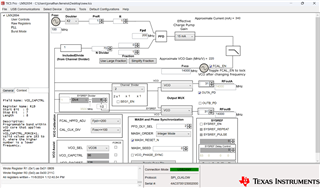

我已将 TICS Pro 实例配置为与 PLLatinum 仿真相同、但我将获得严重杂散的输出:

我认为我的设置没有任何问题(验证输入基准足够无噪声、使用 LDO 消除评估板的电源噪声、板载 LED 变为绿色、表明 PLL 正在锁定)、我看到的唯一可能导致输出信号下降的因素是我配置 TICS Pro 的方式。 我在设置中是否遗漏了任何内容或复制了 TICS Pro 中的 PLLatinum SIM 配置、这些内容可能会导致输出信号严重下降? 如果没有、那么还有什么可以解释此类行为?