Other Parts Discussed in Thread: TMAG5273, LMK1C1108

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK1C1108 主题中讨论的其他器件:TMAG5273

工具与软件:

嗨、团队:

我正在考虑使用21 LMK1C1108将 SCL 从一个 FPGA 分发到161个 TMAG5273。

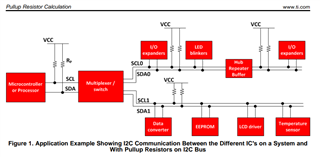

问题1。 每个输出是否都需要上拉电阻器? (它进入 TMAG5273)

它是否应该按照下图所示进行连接?

https://www.ti.com/lit/an/slva689/slva689.pdf

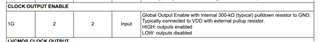

问题2: 1G 是否需要上拉电阻器? (数据表中说"通常使用外部上拉电阻器连接到 VDD "、但仅用于确认。)

此致、

广目