Other Parts Discussed in Thread: CDCE913, CLOCKPRO

Thread 中讨论的其他器件: CLOCKPRO

工具与软件:

大家好!

我们计划 在重新设计时使用 CDCE913来代替已经停产的器件。

它用作 C2000微控制器的主时钟源。

要求提供19.0至20.0 MHz 之间的任何频率、步长为5kHz、并以高达50Hz 的速率在该范围内的2个任意频率之间切换、而不出现干扰或频率过冲。

PLL 时钟源为20 MHz XTAL。 CDCE913似乎 适合于此种应用。

但是、我们并不事先知道所需的频率、即我们必须"即时"计算微控制器中的 PLL 寄存器设置。 因此、我们无法使用 TI ClockPro 来预先计算寄存器数据。

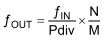

根据数据表中的信息、我们可以计算给定 Pdiv、N 和 M 的 N、P、Q、R 和 Pdiv 寄存器数据

但对于大多数 频率、 Pdiv、N、M 的多个组合可产生所需输出。 选择哪一个?

问题1. :是否有一份文件描述如何为给定的 fin 和 fout 选择 Pdiv, N, M ?

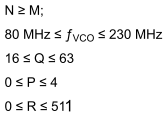

问题2. : Pdiv、N、M 的所有可能的组合只要符合以下限制,都能正常工作:

我们的做法如下:

使用固定值 Pdiv1 = 8和 M = 500并将 N 在3800 至4000范围内变化、以获得19.0至20.0 MHz 输出(即使以5kHz 为步长)。

fVCO 以40kHz 的增量在152至160 MHz 下运行。

问题3. :这能起作用吗?

我在一些频率下试用了 TI ClockPro、以便将结果与我们的方法进行比较。

ClockPro 似乎试图最大程度地 提高 Pdiv、或许是为了改善抖动性能、与我们的简单方法相比、产生不同的结果。