工具与软件:

您好!

我们在使用 DPLL3的基准输入配置、该配置似乎消除了其锁定状态信号的丢失。 在测量基准输入和相对输出时、我们似乎无法正确看到它们的锁相。 DPLL 状态寄存器和显示输出/输入已锁相之间是否存在关系? 配置中是否缺少有助于调整反馈系统频率/相位以保持输出锁定相位的东西?

e2e.ti.com/.../LMK5B_5F00_tics_5F00_pro_5F00_BP_5F00_v7.tcs

谢谢!

Tom

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

我们在使用 DPLL3的基准输入配置、该配置似乎消除了其锁定状态信号的丢失。 在测量基准输入和相对输出时、我们似乎无法正确看到它们的锁相。 DPLL 状态寄存器和显示输出/输入已锁相之间是否存在关系? 配置中是否缺少有助于调整反馈系统频率/相位以保持输出锁定相位的东西?

e2e.ti.com/.../LMK5B_5F00_tics_5F00_pro_5F00_BP_5F00_v7.tcs

谢谢!

Tom

您好、Tom、

我认为这是一个连续的前一个线程: https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1469348/lmk5b33216evm-dpll3-no-input-selected-lopl-lofl-status-no-holdover。

您是否能够使用我在上一主题中提供的配置使 DPLL 锁定? 或者该配置是否也显示 DPLL 锁定切换?

此致、

Jennifer

您好、Tom、

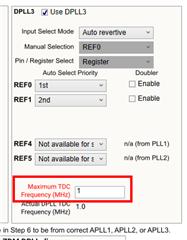

很抱歉、前面的配置未计入 IN1。 我已经修改了配置、以便将 TDC 速率更改为1MHz、从而 DPLL 可以使用相同的 DPLL FB 分频器锁定到48MHz 和125MHz。 1MHz 是两个输入频率中的 GCD。

可以在开始页面中强制设置最大 TDC 速率:

如果这有助于您、请告诉我:

此致、

Jennifer