工具与软件:

设置:、

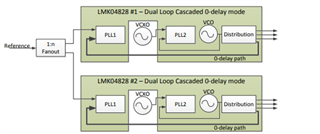

对于两个 LMK04832、其中一个处于单环路0延迟模式(.. 主站参考设计 )和另一个处于分布模式( 从机 )并且两者都使用 CLKin1。

主器件获取100MHz REF、而从器件获取主器件的输出时钟、例如156.25MHz 处的 CLKout8

2.主器件和从器件均通过该引脚获得相同的同步信号

问题:

1.将器件时钟和 SYSREF 输出同时从主器件和从器件对齐是否可行?

2.在此设置中是否特别需要进行任何寄存器设置?

谢谢你。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

设置:、

对于两个 LMK04832、其中一个处于单环路0延迟模式(.. 主站参考设计 )和另一个处于分布模式( 从机 )并且两者都使用 CLKin1。

主器件获取100MHz REF、而从器件获取主器件的输出时钟、例如156.25MHz 处的 CLKout8

2.主器件和从器件均通过该引脚获得相同的同步信号

问题:

1.将器件时钟和 SYSREF 输出同时从主器件和从器件对齐是否可行?

2.在此设置中是否特别需要进行任何寄存器设置?

谢谢你。

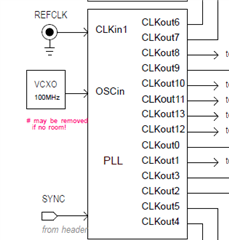

请参阅有关 PLL 的 SCH。 CLKIN0从板载100M VCXO 连接到100M OSC 和 OSCin。

它在2021年由 TI 进行了审查。

我们使用 CLKin1、不使用 CLKIN0或 OSCin、因为单环路之外需要分配模式。

关于 PLL SYNC 引脚、它通过或门连接到外部或 FPGA。

当来自 FPGA 时、SYNC 信号可通过另一个连接器来自外部源、并在 FPGA 内重新计时。

PLL OSCout 可以来自 FBMUX。

实际上、大约半年前我使用 SYNC_POL 运行、但现在无法使用相同的 FPGA 和 PLL 寄存器来重现。

非常感谢。

您好、Michael:

有更新吗?

我进行了更多有关 SYSREF 相位对齐的测试。

在同一电路板上进行编程后、SYSREF 与 CLKout8 (100MHz)具有相同的固定时间差值 之间的比较 与8.3.1同步 SYSREF 例程。

2.每次通过编程更改来自两个电路板的 SYSREF 相位。

3.明天运行同步 SYSREF 例程,我将用测试结果更新此主题。

非常感谢。

您好!

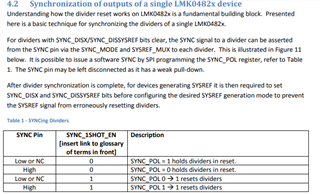

我一直在查看这个论坛和你创建的另一个论坛。 根据我的理解、您想要同步两个 LMK04832、其中一个作为主器件、另一个作为木偶。 两个缓冲器都将接收相同的 SYNC 信号、因此两个缓冲器的输出应相对齐。 这也可以用于切换 SYNC_POL 位。

在我看来、每次通过编程改变 SYSREF 相位都很有意义。 发生 SYNC 事件时、它们将仅与时钟输出进行相位对齐。

应在内部触发该结果的寄存器序列为:

0x10200

0x14480

0x10A00

0x11200

0x11A00

0x12200

0x12A00

0x13200

0x14081

0x14400

0x13900

0x14319

0x14339

0x14319

0x10420

0x10C20

0x11420

0x11C20

0x12420

0x12C20

0x13420

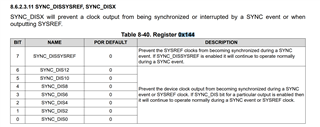

然后、您应重新启用 SYNC_DISSYSREF (0x14480)并将 SYSREF_MUX 设置回3 (0x13903)

如果您没有完整的时钟树、我很难为您提供适当的配置。 您能否为我提供有关每个电路板用作输入和输出的频率的完整概述?

此外、在同步事件之前和之后、您是否能够为我提供时钟和 SYSREF 输出(只需要其中一个)的示波器屏幕截图?

谢谢!

Michael

您好、Michael:

#1

我执行了与上面以及下面相同的例程、该例程来自 TICS Pro v1.7.7.9。

在切换 PLL SYNC 引脚之前和之后、SYSREF 输出仍然未对齐。 我对寄存器0x44有疑问、为什么它设置为0x80而不是0xFF?

0x010200、

0x0144FE、

0x010200、

0x0144FE、

0x010A00、

0x0144FC、

0x010A00、

0x0144FC、

0x011200、

0x0144F8、

0x011200、

0x0144F8、

0x011a00、

0x0144F0、

0x011a00、

0x0144F0、

0x012200、

0x0144E0、

0x012200、

0x0144E0、

0x012A00、

0x0144C0、

0x012A00、

0x0144C0、

0x013200、

0x014480、

0x013200、

0x014480

#2

我还使用 SYSREF 作为1.25MHz 的反馈时钟、使用3.125MHz 并将 SYSRED DDLY_PD 设置为"1"进行了测试。 两个相位仍然没有对齐。

非常感谢。

#3.

1.请附上两块板的 SYSREF。

在切换 PLL SYNC 之前和之后的相位增量相同。

3.向两个板传输相同的 PLL SYNC 信号。

4.但是每次设定 PLL 时、相位增量会有所不同。

非常感谢。

尊敬的 New2Day:

Michael 现在很好、所以我会协助你。

请提供一个简要方框图/时钟树、其中包含您在此处尝试执行的所有频率、以便更好地为您提供帮助。

我知道您需要同步两个 LMK04832、一个作为主器件运行、另一个输出在分配模式下馈送到另一个 LMK04832、而且您需要两个器件的所有输出同步。

通常、您需要为这两个器件共享同步信号。

实际上、如果不首先执行同步事件、就无法在第一个器件上生成 SYSREF 输出。

此致、

Vicente

您好、Vicente:

1.请看下面的图,每块板一个 PLL。

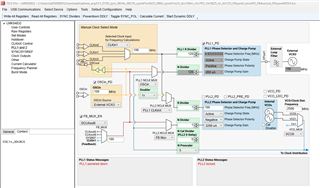

2. TCS 文件也已附加。 指示我当前正在测试的配置之一。

PLL 将处于单环路0延迟模式、从而为 CLKin1提供相同的100MHz 时钟参考(相位对齐)。

没有主器件或从器件关系。

非常感谢。

尊敬的 New2Day:

没有主器件或从器件关系。

[报价]如您所说-您只需第二个器件用作缓冲器。

您只关心主器件的输出同步是不是正确?

我看到您有一个100MHz VCXO -我假设 CPout1驱动的是正确的吗?

我看到您将 SYSREF 分频器设置为反馈。

您是否可以尝试将 CLKOUT6设置为反馈?

这将使其中一个 100MHz 输出被反馈到100MHz PFD。

您仍然可以使用输出-反馈在内部发生。

在您提供的配置中、您启用了所有同步禁用位。

因此、换句话说、您会阻止所有输出和 SYSREF 分频器从 SYNC 本身。

尝试我提供的这一新配置。

同步事件现在应该会为您提供确定性的相位。

您使用的是 EVM + TICSpro 还是您自己的电路板和定制控制器?

此致、

Vicente

您好、Vicente:

#1

要明确说明-每个电路板上的 PLL 将设置为单环路0延迟模式。

前面(上述)处于分配模式的从站无法使 SYSREF 输出相位对齐、这是因为它并不需要模式。

#2

我正在 TICS Pro 的帮助下使用客户电路板。

我已尝试将 CLKout6和 CLKout8都用作 FB 时钟。 无法使 SYSREF 输出对齐、也无法使 CLKout10/CLKout12对齐。

因此、我将尝试改用 SYSREF 作为 FB 时钟。 但是、仍然无法使 SYSREF 输出对齐(0相位差)。

每次编程时、SYSREF 输出之间的相位差都会变化、并且通过切换 SYNC 引脚没有变化。

#3.

我之前附加的 TCS 文件位于同步分频器例程之前。 请参阅上面的 SYNC 分频器例程以及在 SYNC 引脚同时从低电平切换到高电平然后再从低电平之前的三次寄存器写入。

0x014093、

0x014400、

0x013900、

SYNC 引脚恢复为低电平("0")后、点击 SYNC Divider 按钮时 TICS Pro 建议的以下寄存器写入将发生。

唯一的区别是寄存器0x144 (下面的红色)、它显示来自 TICS Pro 的0x014480。 不过、当0x144 = 0x80时、SYSREF 和时钟输出不稳定(这也是我的问题、请参阅上文的内容)。

0x010C20、

0x011420、

0x011C20、

0x012420、

0x012C20、

0x013420、

0x0144FF、

0x014311、

0x013903

非常感谢。

尊敬的 New2Day:

1.已了解-只需要两个在单环路 ZDM 模式下运行且具有相位对齐输出的 LMK04832。

您就可以共享将非常有用的时钟树。 从您展示的原理图中、我不知道这两个板是如何连接在一起的、或者它们是否共享基准、您需要两者上的输出相对于基准时钟具有确定性。

2.

我已尝试将 CLKout6和 CLKout8都用作 FB 时钟。 无法使 SYSREF 输出对齐、也无法使 CLKout10/CLKout12对齐。

[报价]当您尝试了这两种方式时-在执行同步事件之后、您是否有确定性的相位?

很多时候、由于外部因素、例如由于布局而导致的电路板传播延迟、您的输出不会进行相位对齐。

如果每次具有确定性相位(不一定是对齐的上升沿)、则同步事件将成功。

我将 CLKOU8用作 FB_MUX、它能够获取 确定性的 每次在 DCLKOUT 和 SYSREF 之间切换时相位。

现在、它们没有边沿对齐、但您可以使用数字延迟来解决这一问题。

R324 (0x144)控制以下各项:

当我按下"SYNC divider"时、可以获得稳定的连续 SYSREF 输出。

您能告诉我您在做什么的分步流程吗? I

此致、

Vicente

首先、我想从两块板获得所有时钟和 SYSREF 输出 相位一致、 这意味着0相位差、例如所有 SYSREF 输出。

1.我们的时钟树非常简单、LMK04832采用单环路0延迟、并以 CLKin1作为参考时钟输入(不使用 CLKin0和 OSCin)

2.两个电路板是相同的、因此 LMK04832的输入或输出的 PCB 布线等也是相同的

3.两块板都得到 是相同的100MHz 参考时钟 CLKin1 使相位在 CLKin1上对齐

4.同步分压器例程遵循 TICS Pro、切换 PLL SYNC 引脚而非0x0143位[5]、具体如下所示和上文所示。

0x010200、

0x0144FE、

0x010200、

0x0144FE、

0x010A00、

0x0144FC、

0x010A00、

0x0144FC、

0x011200、

0x0144F8、

0x011200、

0x0144F8、

0x011a00、

0x0144F0、

0x011a00、

0x0144F0、

0x012200、

0x0144E0、

0x012200、

0x0144E0、

0x012A00、

0x0144C0、

0x012A00、

0x0144C0、

0x013200、

0x014480、

0x013200、

0x014480、

0x014093、

0x014400、

0x013900、

切换 PLL SNYC 引脚(LOW-HIGH-LOW)

0x010C20、

0x011420、

0x011C20、

0x012420、

0x012C20、

0x013420、

0x0144FF、

0x014311、

0x013903

5.您是用一块还是两块电路板进行测试的? 对于两个电路板、如果在 SYNC 例程之后将0x144保留为0x80、则之后两个电路板的 SYSREF 不会相互锁定。

为什么需要将0x144设置为0x80、而不是0xFF? 谢谢你。

New2Day、

我假设时钟树看起来是这样的、但处于单环路模式。 您能确认吗?

在这种情况下、一旦所有 PLL 都锁定、所有 SYSREF 时钟以及所有具有(最大公共分频值) GCD (SYSREF 频率、时钟频率)=至 SYSREF 频率(前提是 SYSREF 频率小于时钟频率)的时钟之间将具有确定性相位。

如果您要共享所需的输出频率、我们可以确认此配置是否有效。 但是、假设您只需通过这些器件来实现同步、即同步输出分频器。

如果您有任何其他具体问题、请告诉我。

此致!

会的