Other Parts Discussed in Thread: DAC8562

工具与软件:

我们有一个正在开发中的新产品、使 DAC8562正常工作会出现一些问题。 这是数据表: https://www.ti.com/lit/ds/symlink/dac8562.pdf?HQS=dis-dk-null-digikeymode-dsf-pf-null-wwe&ts = 1740129067155&ref_url=https%253A%252F%252Fwww.ti.com%252Fgeneral%252Fdocs%252Fsuppproductinfo.tsp%253FdistId%253D10%2526gotoUrl%253Dhttps%253A%252F%252Fwww.ti.com%252Flit%252Fgpn%252Fdac8562

从数据表中我们收集到可以:

- 使用同相时钟极性-第9页。

- 预计采样会在时钟周期的下降沿发生。 -第9页。

- 选择200kHz SPI 时钟就可以了 -第9页。

- CLR 引脚永久接地没有问题 -第9页。

- 由于 Vout 只有在 CLR 变为低电平时看起来才会变为低电平、因此可以将其永久接地、因为它只会变为低电平一次。 经过 24个时钟周期后、它应该无关紧要。 第8.4.5段

- 长期接地 LDAC 没有问题-第35页

- "在同步模式中、数据在第24个 SCLK 周期的下降边沿上被更新、此边沿之后是一个 SYNC 的下降边沿。 对于这样的同步更新、不需要 LDAC 引脚、在向器件发送命令前、它必须被永久地接至 GND 或者被置为有效并保持低电平。"

- 只需在 VREF 引脚上放置一个电容器、因为我们将使用内部基准。 -第34页

- 我们首先要写入的是使用内部基准并将增益设置为2的命令。

- [0x38、0x00、0x01]或0b00111000 00000000 00000001 -靠近底部的页面38。 是最后一条命令。

- 应立即开启我们的 VREF。 (几微秒)

我们使用 VREF 上的电压来衡量"工作"的指标。 因此、如果 VREF 变为2.5V、那么它将正常工作、如果它保持在0V、那么它将无法工作。

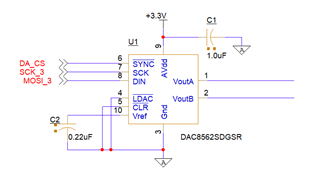

这是我们使用的原理图:

我知道 SYNC 引脚和"芯片选择"不同、但对于我们的意图、降低意味着我们在与它通信、升高意味着我们不在与它通信、这已经足够接近了。

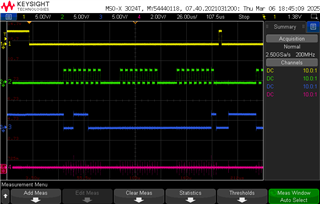

以下是我们发送到芯片的图片:

顶部黄色:芯片选择/同步

绿色:时钟

蓝色:MOSI

底部粉色:Vref (但缩小了一点、因此即使此图像中它始终为0、也更容易看到)。

这是上电后、该芯片选择变为低电平、所以没有其他东西与它通信、它应该处于已知状态。

我预计图中为该 DAC 芯片提供的信号会打开 VREF。 但 VREF 保持低电平(即使器件进入稳定状态后、例如在多秒后)。

有没有我们遗漏的东西? 我希望获得反馈。

--------------------------------------------------------------------------------------------

其他信息:

- 软件 SPI (位拆裂)工作。 我能够通过使用主 CPU 而不是我们微控制器中内置的硬件外设命令引脚开关来控制 DAC。

- 我们使用的是 ATSAME54P20A 微控制器。 这些是 数据表

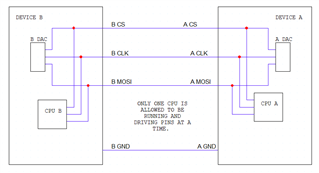

- 我们以前实际上在一个较旧的项目上使用过 DAC8652。 让我们将该板称为"A"、并将我们正在开发的新易出问题的板称为"B"

- 我们已经排除了 PCB 布局错误

- 最重要的是、通过使用已知正常的"A"板并将"A"板上的 SPI 线路连接到"B"板、"A"板可以正确控制"B"板上的 DAC。

- 请告诉我、这项测试对您是否有意义、或者您是否想了解更多信息。 我有很多关于这方面的信息,但不想混乱这篇帖子

- 示波器无需断开任何连接(以排除错误放置物品的人为错误)即可观看通过这些 SPI 线路传输的内容

- 布线"非常非常"接近、这意味着就 SPI 协议而言、它们是相同的。 我把它们重叠在一起、所以如果您想看到它们、请告诉我。

- 他们是如此接近,他们是无法区分90%的它接近终点。

- 如果您很好奇并想分析数据、我还可以从示波器中获取 csv 和 Excel 文件、只需询问即可。

- 通过检查和仔细检查是否存在短路和断路

- 最重要的是、通过使用已知正常的"A"板并将"A"板上的 SPI 线路连接到"B"板、"A"板可以正确控制"B"板上的 DAC。

- 我们希望通过使用全部4种 CPOL 和 CPHA 组合、能够排除错误的 SPI 配置

- 通过使用与已知良好的"A"板相同的微控制器、我们有望消除微控制器配置方面的问题

- 它"不应该"重要、但为了防止出现这种情况、我们还先发送了一条"reset"命令、看看这是否有用。 没有。 该命令在第38页靠近底部的位置[0x28 0x00 0x01](它是底部的第7条命令)

- 将 DAC 放入分线板中、并在开发中通过焊线将其连接到电路板。 "A"板可以控制它、但"B"板仍无法查看 HW SPI

- 我们已尝试轻轻地将 LDAC 拉高而不是将其接地。 不工作。 但"A"板仍支持

- 我们尝试了不同的 SPI 速度。 运气差。

- 我们对全部10个引脚进行了仔细研究、以便在与完全相同的芯片(不是同一型号、而是完全相同的硅和塑料、但未拆焊)通信时发现"A"板和"B"板之间的异常或差异、它们仍然相同。 我们将示波器引线尽可能靠近 DAC。