主题 ( LMX2594) 中讨论的其他器件

工具/软件:

您好、

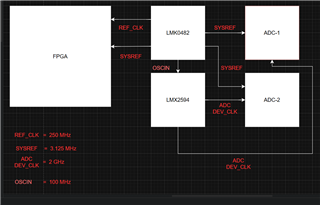

我正在尝试对两个 ADC12DJ3200 IC 的输出进行相位同步。

我通过设置以下参数将 ADC12DJ3200 配置为 JMODE-6(8 位、4 通道,双通道)-

采样频率= 2GHz

ADC DEV_clk = 2GHz

线路速率= 10GSPS

JESD ref_clk = 250MHz

SYSREF 频率= 3.125MHz

我设置了 K = 32 和 RBD = 28。 我从 LMK0482 生成 jesd_ref_clk 和 sysref、并从 LMX2594 生成 ADC 时钟。 两个 ADC 的时钟由 LMX2594 和 sysref 馈送

两个 ADC 都从 LMK0482 馈送。 在示波器中监控时钟是否存在不同的下电上电、并观察时钟是否同步。

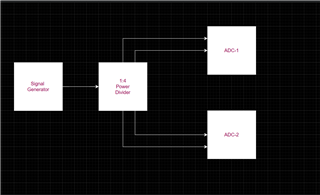

ADC 由 900MHz 输入信号馈送。 绘制 ADC 输出时、可以观察到 ADC 内的通道输出同步、并且 ADC 之间的输出不同步。

我尝试了 SYSREF 位置检测方法进行同步。 两个 ADC 的系统参考位置捕获值不同、其中一个 ADC 的值因运行而异。

ADC-1 -- >系统参考位置捕获值为

0x02C = 1D、0x02D = 07、0x02E = 9C

ADC-2 -- >此 ADC 的 sysref 位置捕获值为变量。

最常见的值是

0x02C = F1、0x02D = FE、0x02E = D9 和

0x02C = F1、0x02D = FB、0x02E = FB

可以观察到、在上述情况下、第二个位始终为零。 因此、我将 SYSREF_SEL 寄存器配置为 1(因为第二位对应于[7:0]中的 1)。 我再次绘制了 ADC 样本

并观察到与以前相同的情况。 尽管 ADC 内的通道输出是同步的、但 ADC 的输出不是相位同步的。

我还尝试了自动 SYSREF 校准方法。 我将 SYSREF_SEL 寄存器设置为“0",“,配置、配置 SRC_CFG 寄存器、然后启用 SRC_EN。 可以观察到 SRC_DONE = 1。

但 ADC 的输出仍然不是相位同步的。

是否需要采取任何措施才能从 ADC 获得相位同步输出?

请请求您解决此问题。

随附 ADC 配置寄存器文件以供参考。