《主题》中讨论的其他器件: ADC12DJ2700和 LMK04832

工具/软件:

尊敬的负责人:

我将使用 ADC32RF55 制作电路板并评估其性能。

我对 SYSREF 的时序和器件时钟有疑问。

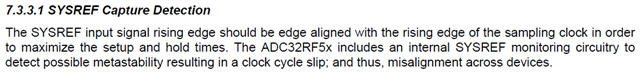

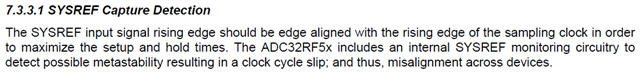

根据 ADC 数据表的第 7.3.3.1 节、似乎意味着 SYSREF 的上升沿应与器件时钟的上升沿一致。 这种理解是否正确?

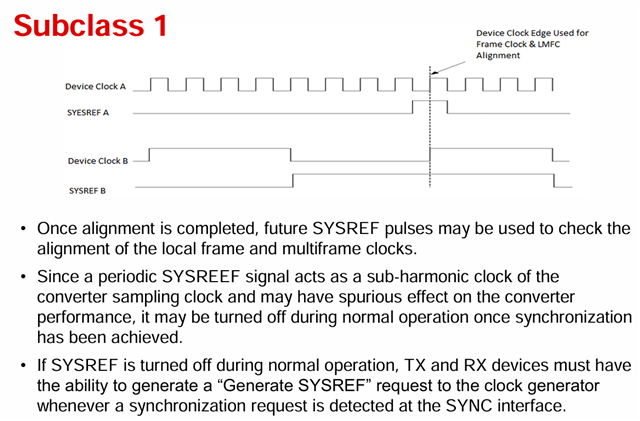

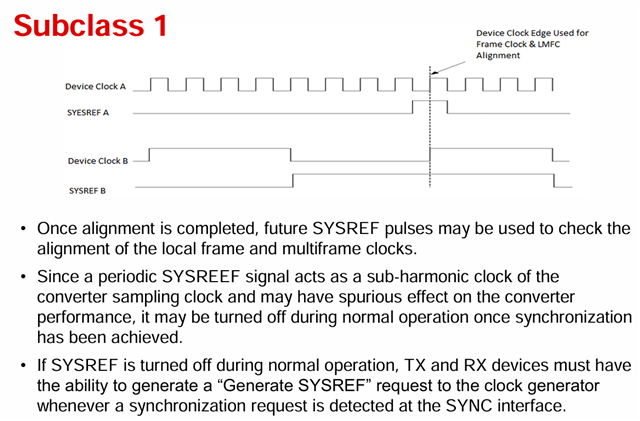

另一方面、通过查看 TI 的其他文档、当器件时钟下降时、SYSREF 似乎正在被触发。

哪一项是正确的?

谢谢你。

此致、

Sayaka Kose

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的负责人:

我将使用 ADC32RF55 制作电路板并评估其性能。

我对 SYSREF 的时序和器件时钟有疑问。

根据 ADC 数据表的第 7.3.3.1 节、似乎意味着 SYSREF 的上升沿应与器件时钟的上升沿一致。 这种理解是否正确?

另一方面、通过查看 TI 的其他文档、当器件时钟下降时、SYSREF 似乎正在被触发。

哪一项是正确的?

谢谢你。

此致、

Sayaka Kose

尊敬的 Sayaka:

对于此器件、sysref 位于上升沿。 您显示的第二张图指示 SYSREFB 在下降沿从低电平变为高电平、因为这是确保从设置/保持时序发生杂散 sysref 的理想时间。 SYSREFB 在时钟上升沿锁存、如图所示。

若要同步 ADC32RF55、您必须为两个器件提供通用 SYSREF 以及源同步时钟输入。 在启动序列期间、该器件在几种情况下需要 SYSREF 来同步内部块。 如果这些块未同时在 ADC 之间同步、则可能无法实现真正的同步。

谢谢、Chase

谢谢您的答复、Chase 先生。

换句话说、SYSREF 的上升沿和器件时钟必须对齐。

我想再问一个问题。

① ADC 数字页面上寄存器 0x22F 的正确值是多少?

我知道 ADC 包含一个 SYSREF 监测电路来监测 SYSREF 和器件时钟之间的位置关系。

例如、如果 SYSREF 和器件时钟的上升沿正确对齐、什么值返回到 0x22F? 如何使用该寄存器?

② 校准页面上寄存器 0x298 的 CAL_STATUS 是多少?

ADC 与接收侧 FPGA 之间的 JESD 通信不正常、当读取 0x298 的值时、会返回 0x1、因此我假设校准未完成。

我知道 0xE 是正确的值、但校准失败时返回的值是否有任何意义? 换句话说、0x1 表示什么?

我很抱歉问一个基本问题、但“校准已完成“的情况到底是什么?

谢谢、此致、

Sayaka Kose

我想再问一个关于 ③ 的问题。

我设计的电路板上的 ADC 似乎未能通过校准。

故障的原因可能是什么?

此外、尽管器件不同、但校准是通过增加工具在以下主题中的延迟输出来完成的。

上述解决方案对 ADC32RF55 是否有效?

Sayaka、如果您使用的是单个器件、那么系统边缘和监控无关紧要、除非需要为链路启动提供确定性延迟。 您可以将系统参考单独监视。 它将报告您监视的系统参考窗口在该实例中的任何内容。 它不是粘滞位、这意味着您连续两次读取它、可能会产生不同的结果。 数据表中有一个完整的部分、用于说明系统参考窗口化功能(如果您对使用该功能感兴趣)。 这适用于相对于采样时钟具有较慢 sysref 边沿的系统、可以用于调整与 ADC 内部 ADC 时钟的 sysref 关系。

仅当不存在采样时钟或在校准期间读取了校准状态读回时、校准才会失败、这意味着您没有等待足够长的时间才能读回。 这很可能是由于 SPI 控制器中的延迟实现不正确所致。 该寄存器低 4 位除 0xE 以外的任何值都意味着校准失败或未完成。 校准正在完成意味着 ADC 的内部校准环路已收敛并已稳定。 因此、在序列结束时需要更长的延迟、因为校准环路需要一段时间才能稳定。

ADC12DJ2700 与 ADC32RF55 没有任何共同之处。 使用 GUI 工具的延迟、每次都会使 ADC 通过校准。

谢谢

感谢您的答复、

我了解了 SYSREF、谢谢。 另一方面、我不了解校准、想问您。

在我们的系统中、使用 FPGA 配置 LMK04832 和 ADC32RF55。

LMK 和 ADC 上电后、FPGA 首先将配置序列写入 LMK。 从 LMK 输出采样时钟 (2.5GHz) 和 SYSREF(关于 1.22MHz) 并且)并且 FPGA 确认 LMK 内的 PLL 是稳定的后、将设计序列写入 ADC。 此时、我们使用 GUI 工具的寄存器输出来写入 ADC。 但是、该工具的延迟输出为 0.1s、因此我们将其更改为 1s 并使用它。 这是正确的吗? 当采样时钟为 2.5GHz 时、该工具会等待大约 1.5s 的校准等待时间、因此我们系统包含 1.6s 的校准等待时间。

我认为评估板也会在写入 LMK 后写入 ADC。 写入之间的近似延迟是多少? 我想知道采样时钟输入与将设置写入 ADC 之间的合理延迟时间。 (当然,我知道我们需要考虑电线长度延迟等因素,因此近似值可以满足要求。)

此外、EVM 的 ADC 寄存器的 SPI 通信频率是多少? 我们的系统以 1MHz 进行通信。 此值是否可能太早或太晚?

非常感谢和尊敬、

Sayaka Kose

尊敬的 Sayaka:

该工具在最后一次 LMK 寄存器写入和第一次 ADC 寄存器写入之间平均需要 223ms。 GUI SCLK 频率约为 3.75MHz。

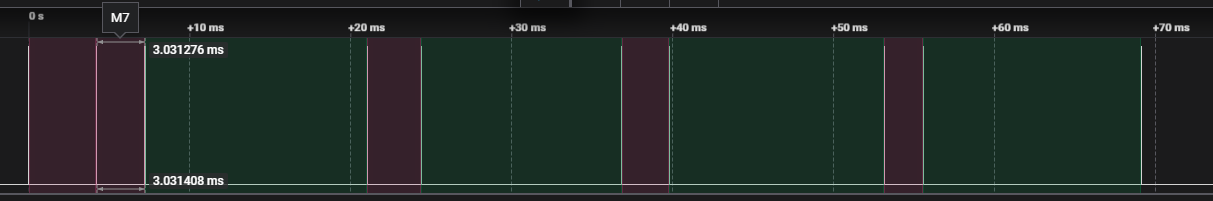

但是、由于我们的工具会在任何顺序 SPI 事务之间产生最小延迟、因此为每个寄存器操作调用 DLL 的性质大约是 3ms。 由于在发生下一次寄存器写入之前增加了读取和修改步骤、因此如果必须操作寄存器、任意两个寄存器写入操作之间的延迟约为 16ms(红色+绿色区域)。

下面的事务显示以下序列:

因此、如果仅使用生成的寄存器序列、则任何两次顺序写入的 GUI 事务平均每 3ms 发生一次。

我刚刚添加了一个功能、使导入的序列现在比以前快得多。 我没有在两次寄存器写入之间出现相同的 3ms 延迟、而是这样做的、现在我可以按块执行寄存器操作、而不会多次调用 DLL。 这使得对 ADC 的顺序写入现在延迟 1us、是 1us。 这仍可用于对 ADC 进行编程、性能符合预期。 我认为您遇到的任何问题都是与时钟相关的、或者再次与延迟问题有关。