您好,

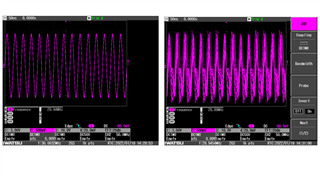

我的客户在 自己的主板上使用 DAC5688。 它们有时会得到左下方所示的良好波形,但有时不像右下角所示。 请告诉我您认为问题的根源是什么?

当他们获得正确的密码时, 只有当他们执行硬件重置或 PLL_SLEEP (CONFI26 0x0d -> 0x0E -> 0x0d)时,密码才会恢复正常。 我的意思是,当他们得到一个好的,他们可以保留它,除非他们进行硬件重置或 PLL_Sleep。 当它们出现异常时,除非硬件重置或 PLL_SLEEP,否则它们无法将其设置为良好状态。

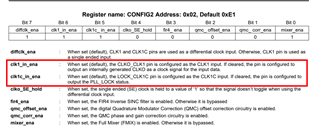

这些是寄存器设置。

地址 数据

0x04 0x00

0x05 0x80

0x06 0x00

0x07 0x00

0x08 0x00

0x09 0x00

0x0A 0x00

0x0B 0x00

0x0C 0x00

0x0D 0x00

0x0E 0x00

0x0F 0x24

0x10 0x00

0x11 0x00

0x12 0x00

0x13 0x00

0x14 0x00

0x15 0x00

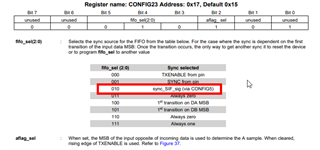

0x16 0x15

0x17 0x00

0x18 0x80

0x19 0x00

0x1A 0x0D

0x1b 0xFF

0x1C 0x00

0x1D 0x18

0x1E 0x13

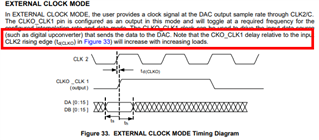

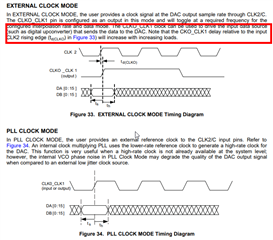

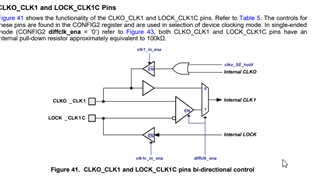

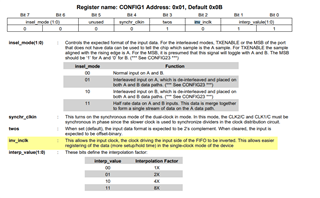

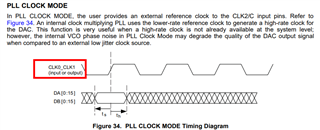

请注意,它们不使用复杂的混音器。 另请注意,他们确认了第45页所示的建议启动顺序,第7页所示的计时(PLL 时钟模式)和时钟输入(CLK2/CLK2C)。 没有什么问题,但有时效果不好。 我想知道原因。

此致,

川崎吉彦津