大家好,团队

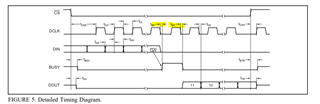

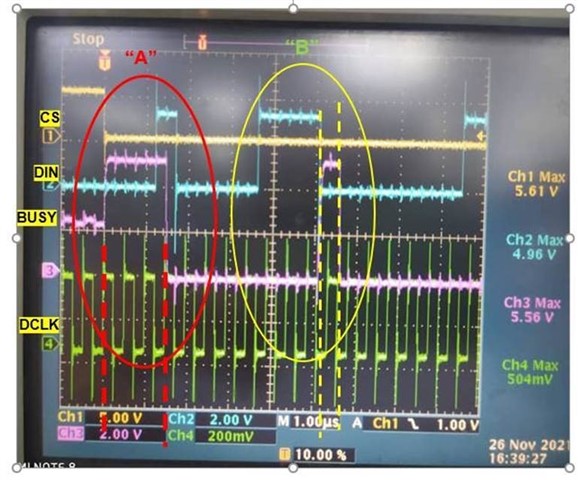

我们对与客户合作期间 SPI 行为有一些疑问。 以下波形是从 ADS7844 SPI 总线捕获的。

- 我们注意到波形在时钟信号的不同边缘改变状态(红色上升边缘和黄色虚线故障边缘)

- 当 ADC 仍处于繁忙状态时,DIN 控制位正在发送到 ADC–可以接受?

- TBD 数据表规格最大值为100ns,而测得的 TBD (波形)为200ns

- TCSS 数据表规格最小50ns 与测得的 TCSS (波形)对比为0ns

如果您想知道 ADS7844将如何响应此类波形,我们会遇到非常间歇性的故障(某些通道上的故障一致,而且在几天后测试时无法重复该故障),我们会希望故障更加一致,请您就此提供建议吗? 谢谢你。

此致,

迈克