线程中讨论的其他部件: ADS1282, ADS1262, ADS1220

各位专家:

我在“TI 精密实验室- ADC”中观看了视频,并从中受益。 但我仍然对实际 ADC 的一些参数及其在设计中的使用情况感到困惑。

至于 ADS1281,我有:

'F_mod'(据我所知的采样率):1 MHz

数据速率:例如1000 SPS。

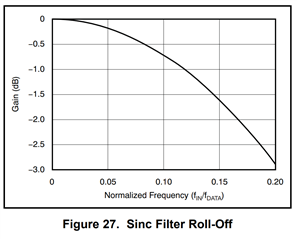

FIR 带宽:0.413 x 1000 = 413 Hz

(我个人对这种 DC 优化的 Δ-Σ ADC 感兴趣,因为它们的 SNR 很高,尽管可能超出了我的需求。)

由于我不熟悉 Δ-Σ ADC 的原理,我对这些参数是否适合我的设计感到困惑,这是我的主要问题。

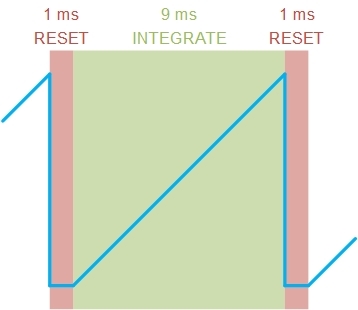

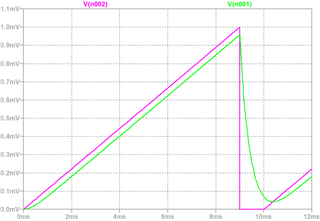

我的输入信号显示如下:

锯齿波的周期为10毫秒,其中9毫秒为“内置”时间,1毫秒为“重置”时间。 我对“整合”阶段的斜坡感兴趣。

这些是我的问题:

1.'f_mod'的1/2是否为“输入信号频率范围”而不存在混叠? 此外,当输入小于1/2 'f_mod'时,能否保证采样精度(与实际瞬态电压相比)?

我的输入信号包含步进组件的上限频率约为30 kHz,比0.5 MHz (1/2 f_mod)小得多,这意味着每个超采样点都是准确的?

2.由于我的信号有步进部分,我可以参考哪些参数来确保调制器的速度可以跟随瞬态电压重置? (例如 OPAMP 中的“露率”? 但我在 ADS1281的数据表中找不到它。)

还是仅取决于输入驱动电路的时间常数? 在这种情况下,我认为这不是正确设计的问题。

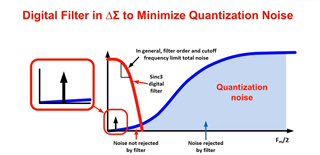

3. FIR 滤波器的低截止 BW 是否会降低我的时间范围采样准确度?

我认为数字滤波器平均(小数)一个输出数据点的超采样点(OSR)为1024个。 因此,在我的计划 A 中,我使用1000 SPS 数据速率来采样我的100 Hz 锯齿波,如下图所示,我假设“所选数据点”应该准确。

(如果我使用宽带 ADC 并获得更多数据点作为计划 B,最终我仍然需要手动平均这些数据点,而不是使用集成的 FIR 滤波器)

但我担心我的设计是否可行,因为我不理解413 Hz FIR 带宽的含义。 我尝试使用具有相同 BW 的模拟滤波器模拟滤波器,导致输出不准确。 那么 FIR BW 意味着什么? 它会影响我的设计准确性吗?

谢谢!