请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:ADS131E06 主题中讨论的其他部件:ADS1278, ADS131E08

大家好,

缓冲器和D触发延迟电路如何工作,为什么可以减少信号延迟?

如果需要放置延迟电路,应如何连接接线? 您是否有接线图?

此致,

罗艾米

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Amy,您好!

感谢您的帖子。

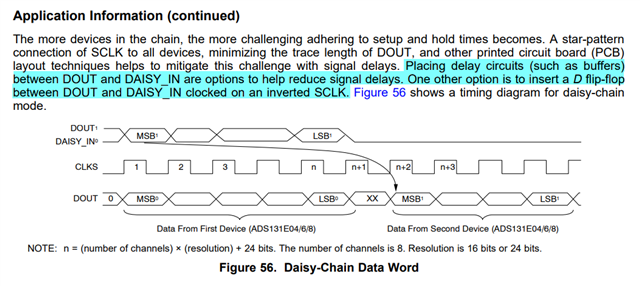

我认为解释这种技术的一个更正确的方法是,当传播延迟相对较大(即接近半个SCLK时间)时,延迟电路(如D触发电路)可以帮助避免数据传输问题。 如果传播延迟相对较小,则不需要此技术。

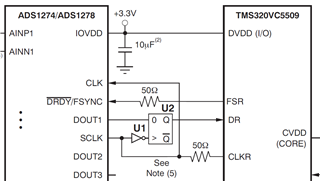

此技术的一个示例可在我们的ADS1278数据表中找到:

当用于数据捕获的SCLK边缘(即ADS131E08的后缘)在下一个DOUT位发生转换和稳定(如MCU所示)之前发生时,较大的传播延迟会导致问题。 这会导致SCLK后缘捕获以前的旧数据 ,而不是固定的新数据。 在这种情况下,具有反向SCLK输入的D触发器可以将数据位保持 额外的半SCLK时间。 结果是MCU继续使用SCLK尾随边进行数据捕获,但每个位都延迟一个完整的SCLK周期,从而确保捕获的数据完全固定。

再次强调-我不建议实施此技术,除非已证明系统中的传播延迟导致了问题。

此致,

Ryan