主题中讨论的其他部件:ADS4249,, ADS5463

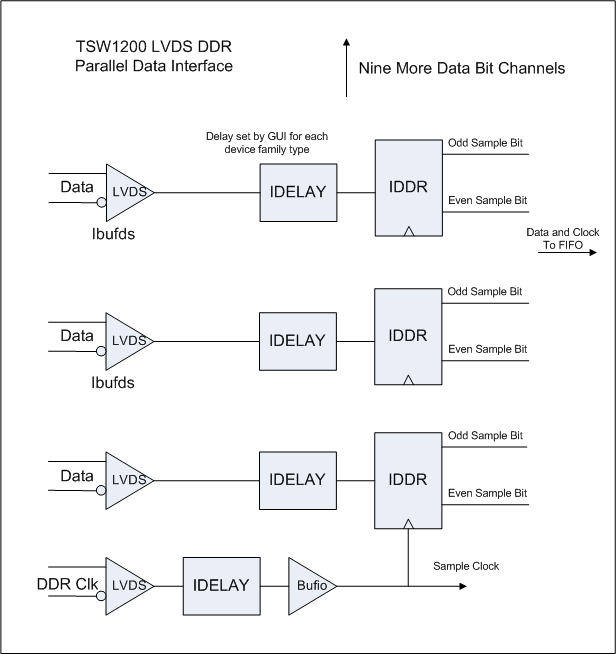

我正在研究 如何将ADS4249EVM与Xilinx 7系列FPGA "VC707"连接起来。 我已根据下面给出的方框图从VC707中的ADS4249接收时钟和数据,但跳过IDELAY部分。数据和时钟分别在IBUFDS和IBUFGDS中接收,并直接发送至IDDR,然后路由IDDR的输出(Q1和Q2) 到FPGA IO引脚以查看结果。

示波器的屏幕截图如下所示:

上图中的蓝色信号是从ADS4249EVM到FPGA IO引脚的输入差分时钟, 橙色信号是从ADS4249到FPGA IO引脚的输入双倍数据速率信号,绿色信号是 来自IDDR的输出SDR信号,后者被路由到FPGA IO引脚。 SDR数据同时具有“高”和“低”两种状态,但我没有得到。

或者必须使用IDELAY甚至是慢速采样速率(即10MHz)

感谢您的期待。

此致