Other Parts Discussed in Thread: ADS5407, DS10BR254

主题中讨论的其他部件:DS10BR254,

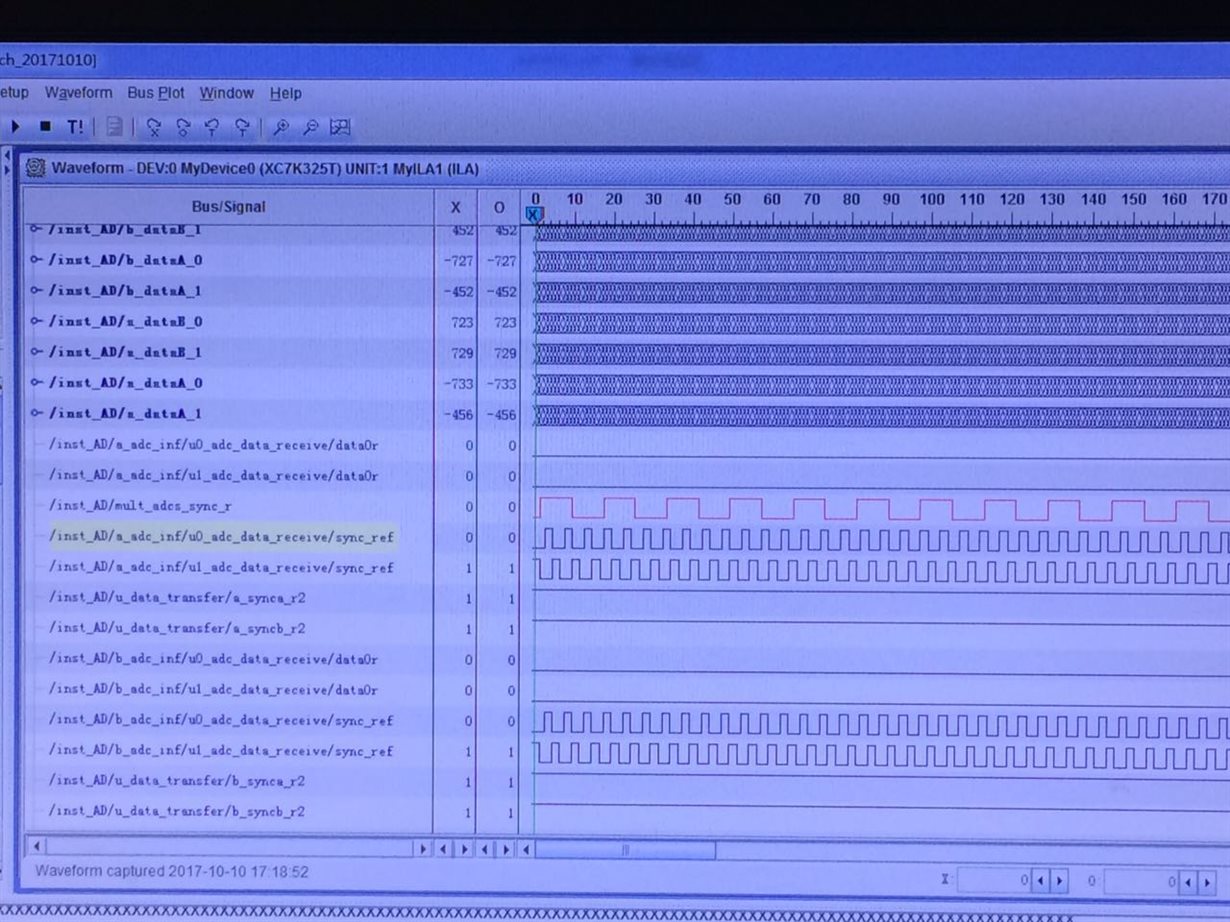

在我的项目中,我必须将16个平台上的64个ads5407与K7 (Xilinx) FPGA同步,现在我遇到了如下问题:

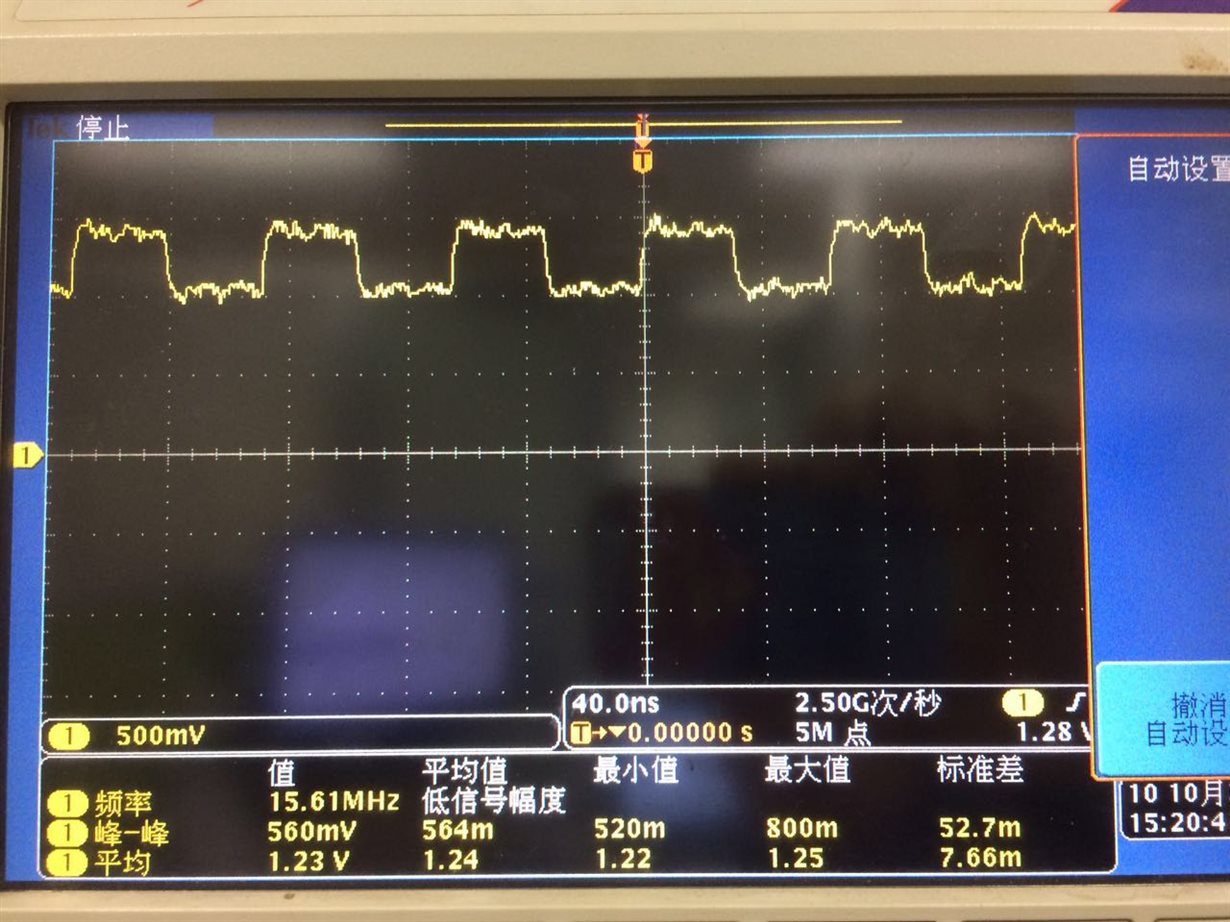

我有通过LVDS缓冲器(DS10BR254)的同步信号来链接到直流耦合中的ADS5407,但我发现SYNCOUT信号不是完美的脉冲序列,因为信号来自ADS5407数据表中提到的5位计数器。

I do set HP Mode=1,(0x01,D1)(我确实要设置HP模式=1,(0x01,D1)

所以我认为ADC没有正确同步,我想我的操作是否有一些错误的步骤?

您可以通过电子邮件与我联系,我的电子邮件 地址是zhouleichen@163.com

谢谢!

ZhouLc.