主题中讨论的其他部件: CDCP1803, SN65LVDS100, DAC3162

尊敬的各位:

我拥有DAC3162EVM和Xilinx AC701 (Xilinx Arix7 FPGA评估板)。

DAC3162EVM和 AC701上的FMC连接器完全兼容。 所以我在连接两块主板时没有任何问题。

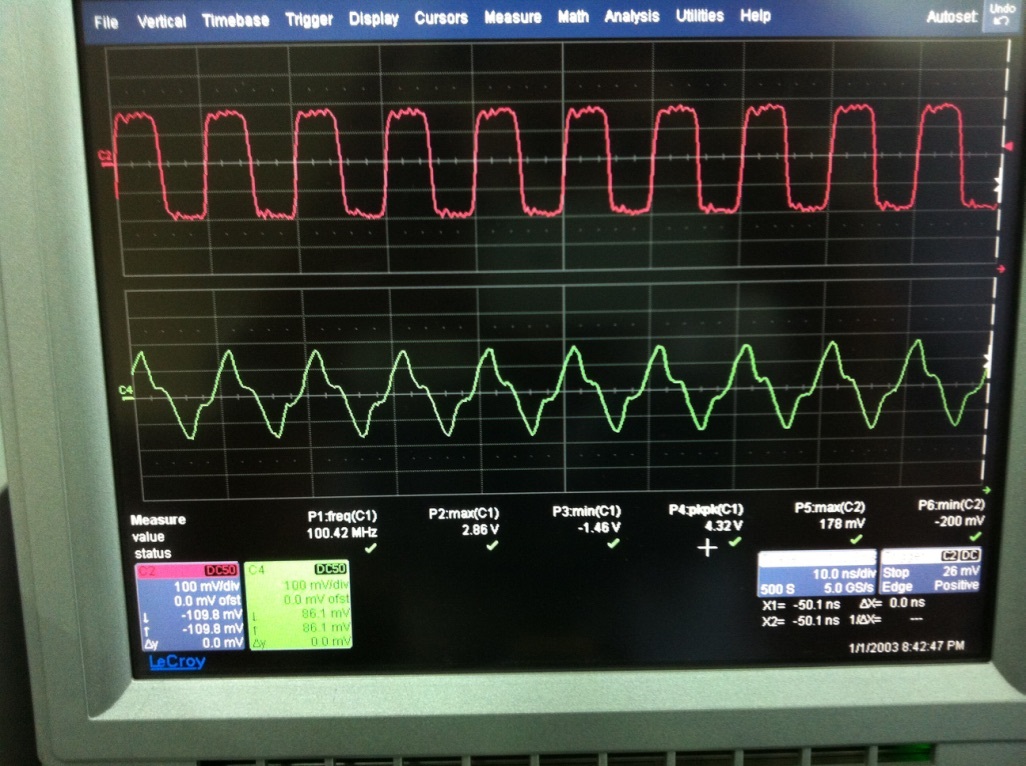

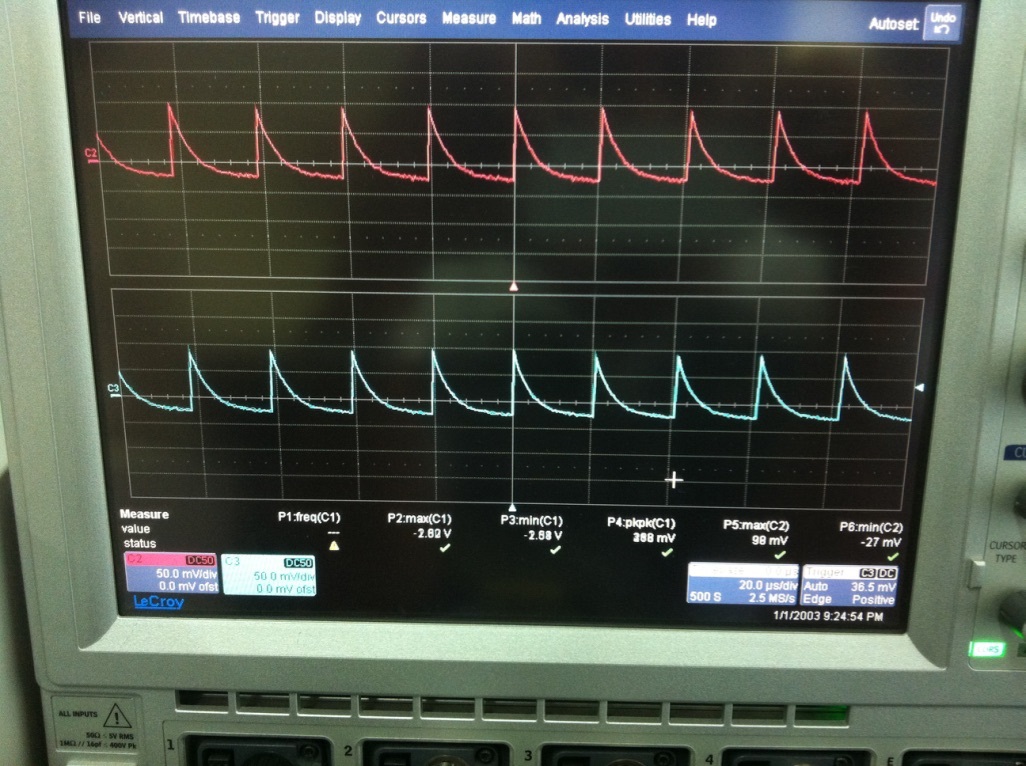

DAC EVM板上具有TI器件CDCP1803。 CDCP1803采用外部时钟信号,并提供DAC Clk,FPGA Clk等。我能够为DAC EVM的J9连接器提供200 MHz外部时钟,还能够在示波器上轻触并查看DAC Clk和FPGA Clk。 到目前为止还不错。

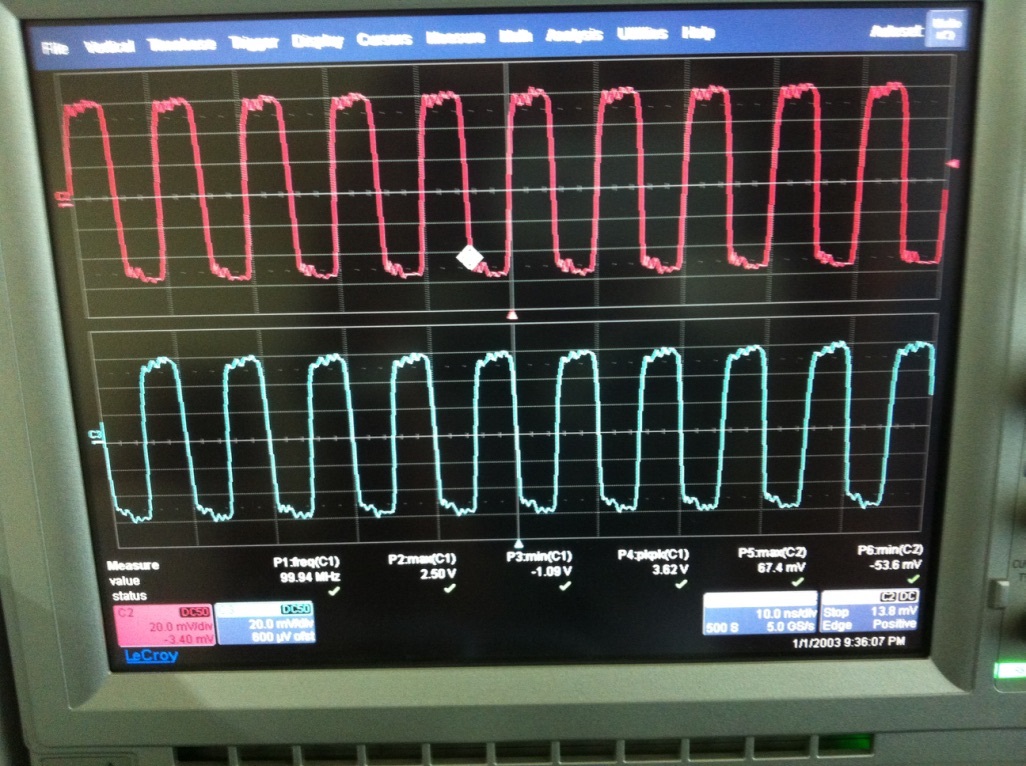

在 DAC3162EVM的FMC连接器上,FPGA Clk (来自DAC3162EVM板) 是LVPECL标准。 我已经测量 了此时钟的电压,发现它们与组件CDCP1803的数据表中的电压相同(Clk_P或Clk_N信号的回转电压为1.5V至2.5 V)。 此FPGA Clk将成为FPGA的输入clk,DAC数据将通过.r.t此Clk输出。 FPGA Clk和DAC Clk的设置速率相同。

现在,虽然Xilinx Artix7 FPGA不支持LVPECL标准,而较新的Xilinx FPGA也不支持LVPECL标准,但我想知道我可以在FPGA中选择哪种其他标准,以便它仍然可以将FPGA Clk (LVPECL)用于Xilinx AC701电路板。

DAC3162EVM板已将FPGA Clk映射/连接到Artix7 FPGA的D19和C19引脚。

等待您的建议。