在“线程: ADS5294”中讨论的其它部件

海防

在ads5263数据表中没有提到如何将其配置为按位模式,在一篇文章中,我读了用0x8100写入0x28寄存器,这会使它变得非常明智,这是否每次都起作用,或者因为我不会这样做而导致任何问题 连续获得输出,写入寄存器两次后,有时会比该次多得到输出,基本上我的输出不稳定,只有当我写入寄存器多次时,我得到输出 是没有任何问题当我们写入8100到0x28时, 还是其他问题,请帮我。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

海防

在ads5263数据表中没有提到如何将其配置为按位模式,在一篇文章中,我读了用0x8100写入0x28寄存器,这会使它变得非常明智,这是否每次都起作用,或者因为我不会这样做而导致任何问题 连续获得输出,写入寄存器两次后,有时会比该次多得到输出,基本上我的输出不稳定,只有当我写入寄存器多次时,我得到输出 是没有任何问题当我们写入8100到0x28时, 还是其他问题,请帮我。

您好,Mohith:

我认为这些设置是正确的0x28 0x8100,应该启用ADS5263中的位模式。

我对设置很确定,因为在另一篇E2E文章中,Chen提到我们已经测试了相同的设置,我也查看了类似的其他ADC数据表,例如。 ADS5294,他们在那里分享了有关此模式的更多详细信息。

我认为这可能是一个捕获问题。 与其他开机自检一样,您能否验证:

1. 您是否正在使用ADS5263 GUI。

2.使用TSW1400 EVM从ADS5263中捕获输出数据时,还需要确保可以加载正确的ini文件 ,以便正确运行高速数据转换器Pro GUI。

谢谢,此致,

Abhishek

您好,Abhishek,

感谢您的回复,

我们正在使用带有ads5263芯片no ads5263 GUI的自定义主板,带有Xilinx Zynq主板并选择I/O IP,请告诉我是否需要处理硬件或固件代码中的任何角落情况,以便不会出现捕获问题。

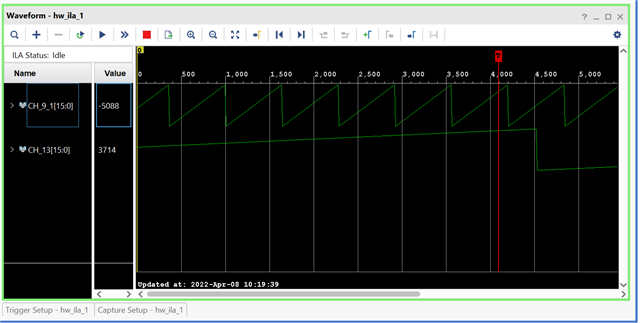

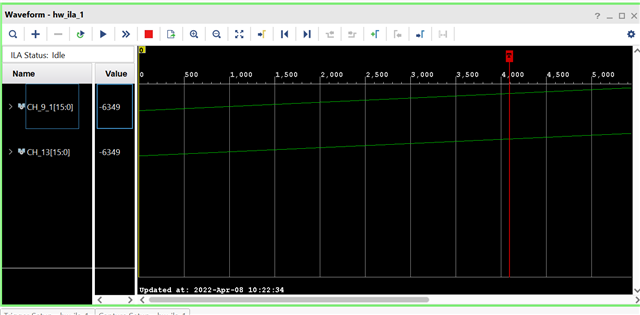

如果我使用具有0x0040数据的寄存器0x25生成斜坡测试模式,我会再观察一次,我总是能够看到斜坡,但每次我写此寄存器时,斜坡变化的样本都没有,我的意思是说斜坡变得更大,有时更小 已附上一些ILA输出剪刀供您参考。

谨致问候

Mohith RS

您好,Mohith:

感谢您分享波形和更多信息。

从我目前为止所能得到的信息来看,这些问题通常与接口或不正确的反序列化有关。 以下要点与您观察到的内容有关:

1.当出现位移或反序列化不正确时,斜坡可能会变得不稳定。 我的意思是说,由于一些错误,在反序列化后,1位不在正确的位置(例如,捕获后,表示顺序以某种方式变为D7...D0,D15,D14..D9,那么每次切换D0时,您将看到2**8代码更改,而不是1代码更改)。 为了验证/消除这种可能性,您可以-

——用自定义数据模式进行测试,只保留1位高REST 0,然后进行捕获,看看您是否看到要捕获的位移动或移动捕获-与我们分享观察结果。

2.每当您更改LVDS输出模式时,另一种可能性可能与FPGA配置有关。 通常,良好做法是在执行输出数据模式更改或序列化因子更改等操作后重新初始化FPGA捕获设置

请告诉我,以上内容是否有帮助,或者您是否得到了一些指示,以确定问题到底出在哪里。

此外,还有一件事,它是发生在多个设备上还是仅发生在这一个设备上? 如果您尚未检查多个设备/主板,我建议您尽可能在多个设备上尝试相同操作。

谢谢,此致,

Abhishek

您好,Abhishek,

谢谢,这次讨论非常发人深省,非常有帮助。

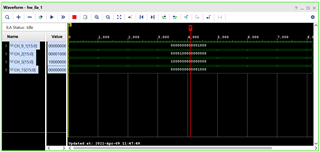

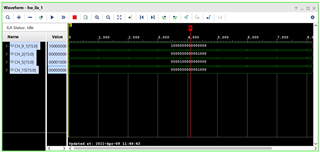

正如您所说的那样,我尝试使用自定义模式,这些设置(0x25,0x0018)和(0x26,0x8000)位在 我每次写入寄存器时都在移动,下面是输出的一些剪切。

是的,所有的芯片都是这样的,我们已经购买了8个芯片,而且所有的8个芯片都是这样的。

是的,每次 我们写入SPI寄存器以更改输出模式时,我们都会重新初始化数据捕获设置。

我 想讨论的另一个观察是,每当 我 执行全局断电 0x0F,0x0200,位都应该初始化为0或全部1,但有时它全部为0,有时它的某些位将成为一个,我也会附加这些剪刀。

如果是因为比特打滑,请告诉我如何避免,或帮助我解决任何问题。

此致,感谢您,

Mohith RS

您好,Mohith:

感谢您分享信息。

我在团队中也讨论过这个问题。

由于所有设备都显示出此位打滑,这表明FPGA 代码实施存在一些问题。 因为设备本身不会更改任何位。

此外,我们还测试了位模式,没有发现任何问题。

我们建议您:

1.检查FPGA中与FCLK (数据与帧时钟的关系)相关的数据对齐情况

2.根据数据分离逻辑重新设计FPGA代码实施。

谢谢,此致,

Abhishek