主题中讨论的其他部件:ADS41B29,

您好,

我们尝试使用ADS41B29将接收的IF信号转换为数字数据。 我们使用 FMC-ADC适配器将ADS41B29EVM连接到Xilinx FPGA板。

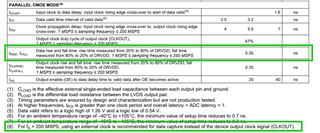

ADS41B29配置为具有250MHz输入时钟的CMOS接口2补码输出。 输入信号(IF)频率 从20MHz到50MHz不等,振幅也不同。 FPGA逻辑还使用250MHz连续采样12位数据。

我们发现数据不稳定,而且会不时发出噪音。 例如,在高振幅数据之后,第10 位应该是低级别,但 该位保持在高水平。 此问题也会发生在其他位中。 我们已使用示波器进行检查。

请提供一些建议/建议以解决问题?

非常感谢。