你好,Im Juan Camilo。

我的DAC5688具有以下配置:

| 注册地址 | 注册数据 |

| 0x01 | 0x09 |

| 0x02 | 0x60 |

| 0x03 | 0x00 |

| 0x04 | 0x00 |

| 0x05 | 0xB0 |

| 0x06 | 0x00 |

| 0x07 | 0x00 |

| 0x08 | 0x00 |

| 0x09 | 0x00 |

| 0x0A | 0x00 |

| 0x0B | 0x00 |

| 0x0C | 0xFF |

| 0x0D | 0xFF |

| 0x0F | 0x40 |

| 0x10 | 0x00 |

| 0x11 | 0x00 |

| 0x12 | 0x10 |

| 0x13 | 0x10 |

| 0x14 | 0x00 |

| 0x15 | 0x00 |

| 0x16 | 0x00 |

| 0x17 | 0x17 |

| 0x18 | 0x80 |

| 0x19 | 0x00 |

| 0x1A | 0x0E |

| 0x1b | 0xFF |

| 0x1C | 0x00 |

| 0x1d | 0x00 |

| 0x1E | 0x00 |

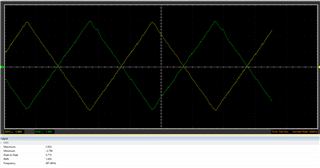

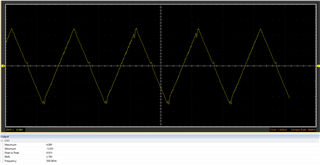

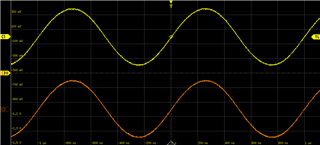

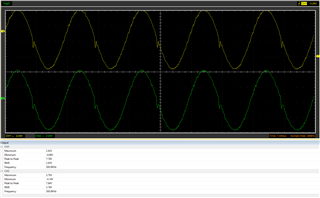

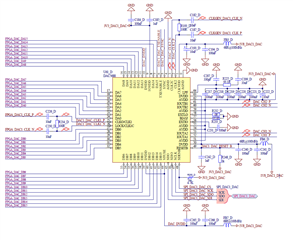

IM执行"建议的启动顺序"一节中的步骤,执行所有这些操作后,TXENABLE信号从低变为高。 我的clk1是单端(250 MHz) CLK2是差分时钟(500 MHz),CLK1,DA和DB 由FPGA提供, 串行接口由PIC提供,RESET,SYNC和TXENABLE。

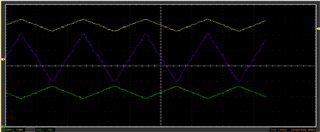

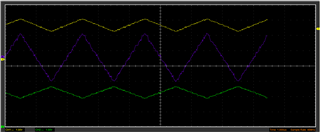

使用 config1的位2 (inv_inclk),我可以将故障从CH1更改为CH2,当此位为“0”时,故障在CH2中,当为“1”时,故障更改为CH1。 我想知道DAC5688上的配置是否正确,或者是否需要修改某些寄存器。

此致,

Juan Camilo Peña A.