您好!

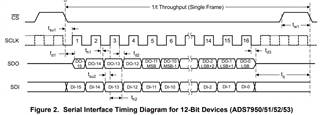

我们使用基于 SPI 通信的 ADS7952 (38引脚 TSSOP 封装)来设置原理图。

此设计中的 SPI 总线与其他从器件共享、其中每个从器件都可以与通信

微控制器。 这意味着在我们的设计中、所有 SPI 从器件都应与其连接

所有 SCLK 信号的情况也是如此。

然而、微控制器的 sel 输出(片选输出)被连接至一个3线至8线多路信号分离器。

基本上,问题是关于 SDO 引脚的:

1)具有 ADS795x 的 SDO 引脚在芯片选择时的默认(固定)定义逻辑电平("0"或"1")

引脚="1"(芯片的 SPI 总线被禁用)?

在共享 SPI 总线中、这意味着 SPI 从器件的每个 SDO 引脚都应连接到某种形式的

输入(或保护)、例如输入多路复用器或 三态缓冲器。

2)一般情况下:TI (所有) SPI 从器件的每个 SDO 引脚应使用某种形式的输入进行连接

(或保护)这种方式?

Thx 提前、

Armand