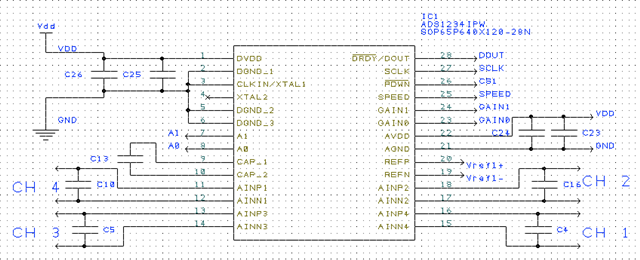

在最近的一批器件中、我们有4个器件中的12个 ADS1234芯片中的7个发生了故障。

4:DOUT 引脚一直处于高电平

-1使 DOUT 引脚持续处于低电平

-其他器件在时钟引脚和 DOUT 引脚之间似乎存在某种内部短路

我们在慢速、10SPS 模式下使用这些器件、我认为我们遵循了所有数据表建议。

ADS1234是否有任何已知的故障模式?

我有一个理论认为、在 ADS1234的电源电压稳定之前、控制引脚上可能会有电压、这是否会导致这种行为?

如果我们能防止这种情况再次发生,我们将非常感谢您的帮助!

A