主题中讨论的其他器件: ADS124S08

您好、E2E 专家、

你好。

- 我不理解"多通道系统"的讨论。 如何在同一信道上使用多个器件而不会发生数据冲突? 该部分仅讨论了所有 DOUT 变为低电平的情况、但未讨论如何从多个器件检索数据。 请尽可能明确。 谢谢!

- "多通道系统"讨论提到了多个器件的使用。 如果我不使用相同的信道、是否正常? 我计划在第1个器件上使用 CLK1、SDO1和 SCLK1通道、 在第2个器件上使用 CLK2、SDO2和 SCLK2通道。 这是否正常?

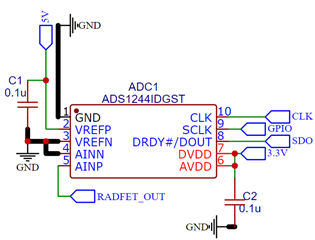

此外、还希望请求对下面的原理图进行设计审查。

此致、

CSC