我正在使用 FPGA (Zynq Ultrascale+ MPSoC ZCU102评估套件(xilinx.com))to)来关闭25MHz 电源转换器、并希望使用高速 ADC 来实现电压模式控制环路。 是否可以将 ADC 的数字输出置于1/25M 以下的 FPGA 中? 和/或从 TI 产品线获取 FPGA 的 ADC 读数最快的方法。 希望得到推荐、并希望相应地购买 EVM 板。

感谢您的帮助、

Patrick

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我正在使用 FPGA (Zynq Ultrascale+ MPSoC ZCU102评估套件(xilinx.com))to)来关闭25MHz 电源转换器、并希望使用高速 ADC 来实现电压模式控制环路。 是否可以将 ADC 的数字输出置于1/25M 以下的 FPGA 中? 和/或从 TI 产品线获取 FPGA 的 ADC 读数最快的方法。 希望得到推荐、并希望相应地购买 EVM 板。

感谢您的帮助、

Patrick

尊敬的 Patrick:

您对 ADC 选择有任何限制吗? 采样率、输入带宽、分辨率、通道数、功耗、 输出接口(LVDS/CMOS)?

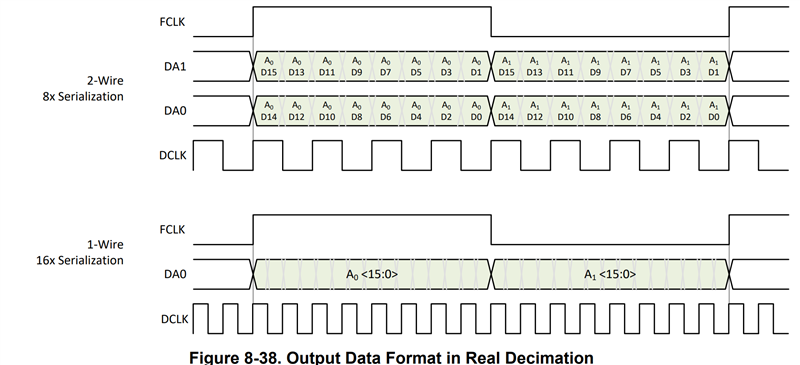

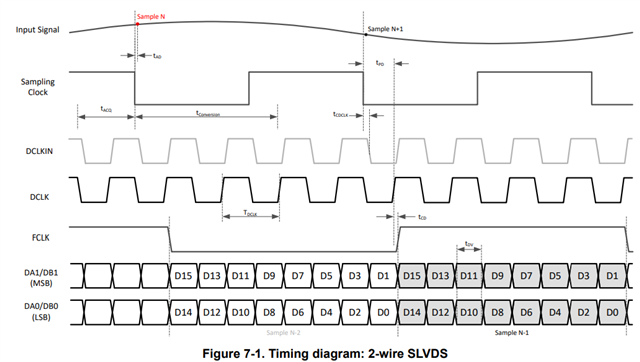

值得关注的一个器件系列是 ADC3663 (65MSPS、双通道)、ADC3662 (25MSPS、双通道)、ADC3663 (65MSPS、 单通道)或 ADC3662 (25MSPS 、单通道)。 这些器件具有一些输出数据速率选项、可实现高于25MHz 的传入采样目标。 这些输出数据格式被称为2线制、1线制和1/2线制模式(特定于双频带)、可实现数据时钟(DCLK)的灵活性。 下图显示了如何使用任一种方法传输两个连续的16位样本。 在相同的时间周期(FCLK)内、2个差分对(2线制模式)或1个差分对(1线制模式)。

此致、Chase

感谢 Chase 回来找我、

我没有任何功率限制。

我只需要1个通道。

带宽具有一定的灵活性、但优先选择大于250MHz 的带宽

输出接口不受限制、我在 FPGA 方面具有很大的灵活性。 JESD204B 也是一个选项。

非常感谢您的选择、ADC 3663看起来是双通道输出的最高采样率、(另请查看 ADC 3664的125MSPS 采样率)。 只是想知道 Xilinx 建议的射频 ADC ( ADC12J4000)由于其 10秒时钟周期的较高延迟而无法工作吗?

最后一个问题、

我只想确保时钟是直的。 有一个采样时钟、 一个帧时钟和一个数据时钟。 采样时钟在采样频率下直观地运行、帧时钟是指数据帧的长度、每个位的数据时钟是多少。 我在数据表中没有注意到数据时钟的最小值或最大值、但它看起来比采样时钟快。 我的 Xilinx 可以在800MHz 频率下运行、数据时钟能否以那么快的速度运行、或者您建议的限制是什么? 我还查看了数据表底部的图表、因此我认为它可以正常工作。

尊敬的 Patrick:

如果可选 JESD 接口、则 ADC12J4000也是不错的选择。 我要提到的是、我们确实为 Xilinx FGPA 提供了免费的 JESD204B/C 快速设计 IP、以帮助设计人员实现 JESD 接口。 有关详细信息、请访问: https://www.ti.com/tool/TI-JESD204-IP

关于 ADC12J4000、延迟为64个时钟周期、远高于 ADC3664的2个时钟周期、但采样时钟也快得多、因此如果以4GSPS 的满速率(2个时钟周期/125MHz=64个时钟周期/4GHz = 16ns)进行采样、则以秒为单位的延迟相同。 但是、该延迟是确定性的、因此在初始"数据管道"满后、输出数据将始终代表16ns 之前采样的数据。

我刚刚与我们的设计团队进行了检查、我们确实有一个 ADC3664单通道变体、它的发布/预览相对较快。 该器件的名称为 ADC3564。 我还询问了数据速率的任何限制、由于内部输出驱动器的最大额定速率约为1Gbps、因此 DCLK 确实有上限 如果您查看2线制、则在14位模式下、DCLK 将为437.5MHz。 在单线制模式下、满足1Gbps 输出驱动器额定值的最大采样率约为70MHz。

如果您有任何其他问题、请告知我们!

此致、Chase