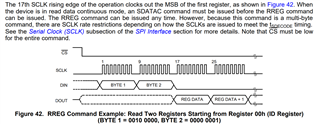

根据数据表的指令、我首先发送 SDATAC 指令、然后延迟2μs μ s (频率为2MHz)、然后发送0x20 0x01 (ID 寄存器地址为00h)、从而产生以下波形。

在我发送数据后、ADS131E08似乎没有任何响应、我想问问题是什么?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

根据数据表的指令、我首先发送 SDATAC 指令、然后延迟2μs μ s (频率为2MHz)、然后发送0x20 0x01 (ID 寄存器地址为00h)、从而产生以下波形。

在我发送数据后、ADS131E08似乎没有任何响应、我想问问题是什么?

尊敬的 Zhen:

感谢您验证计时规格。 我同意 tSDECODE 规范看起来是正确的。 不过、tcsh 是从 CSn 上升沿到下一个 CSn 下降沿的时间。 在您的原始帖子中、它似乎约为3.5 us (足够长)。

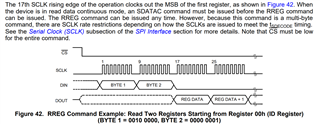

发送两字节命令(0x20 0x01)后、必须再发送两个空字节(0x00 0x00)才能读出寄存器数据。 原始帖子显示了正确的字节序列、但最后一个帖子仅发送 RREG 命令。

您是否看到在启动后切换 DRDYn? 这将有助于确认器件已正确加电。 如果没有、您能否尝试在电源完全斜升后在器件引脚上发出 RESETn 脉冲?

在最后一幅图像中测量的 SCLK 周期可能只是逻辑分析仪捕获带宽的限制。 因此、您可能会注意到一些偶尔出现的误差、这些误差并不代表真正的 SCLK 周期和占空比。

此致、

Ryan

尊敬的 Zhen:

我没有意识到您使用的是我们的 ADS131E08EVM-PDK。 您使用的是 MMB0板还是将外部控制器连接到子板? 如果您使用自己的控制器、我建议断开 MMB0并将外部电源直接提供给测试点或跳线引脚。 请记住使用可用的测试点将外部电源接地连接到 EVM 接地。

如果 DVDD = 1.8V、则将1.8V 外部电源连接到 TP9、并将 JP11跳线配置到[1-2]位置。

对于 AVDD = 5.0V、将5V 外部电源直接连接到 JP1[2](请勿安装跳线)。 此外、将 JP7跳线配置到[1-2]位置(AVSS = AGND)。

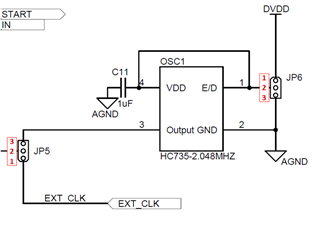

以上电源是使用 SPI 接口所需的电源。 为了开始 ADC 转换、 必须有一个有效时钟(内部或外部)。 要选择2.048MHz 内部时钟、请卸载 JP10上的跳线、使 CLKSEL = 1。 要使用外部时钟源、请将跳线安装在 JP10上的[1-2]位置(CLKSEL = 0)。 您可以使用 OSC1作为外部时钟(JP6[1-2]和 JP5[2-3])、也可以直接为 JP5[2]提供外部时钟(配置 JP6[2-3]以禁用 OSC1)。 假设 START 引脚处于高电平且时钟处于活动状态、您将看到 DRDYn 在以默认数据速率启动后切换。

此致、

Ryan

尊敬的 Zhen:

您在原理图中绘制的引脚标签不正确。 跳线的引脚1由跳线原理图符号中的陷波表示。 请重新检查您的跳线设置。

对于 1.8V DVDD 运行、OSC1可替换为 Sit8002AC-34-18E-2.048器件。 我没有意识到默认器件仅在3.3V 电压下工作。对于您的设置、是否需要外部时钟? 如果您可以使用内部时钟、则可以更轻松地进行评估。 对于内部时钟:

此致、

Ryan

尊敬的 Zhen:

[~ userid="521369" url="μ C/support/data-switchers-group/data-switchers/f/data-switchers-forum/1114346/ads131e08-error-reading-id-through SPI/4140283#4140283"]根据 ADS131E08数据表、如果要使用内部振荡器、不仅需要将 CLKSEL_PIN 设置为1、还需要将 CLK_EN 位设置为1。

[/报价]此陈述不正确。 只要 CLKSEL 引脚为高电平、内部振荡器就被激活。 默认情况下、该内部时钟信号与 CLK 引脚本身是分离的(CLK_EN = 0b)。 但是、如果您希望探测该信号或将其连接到另一个电路、则可以设置 CLK_EN = 1b、并且内部振荡器将被驱动到 CLK 引脚作为输出。

选择内部振荡器且 START 引脚为高电平后、您将看到 DRDYn 引脚切换。 这是确认器件已正确启动的另一种方法。

此致、

Ryan