你(们)好

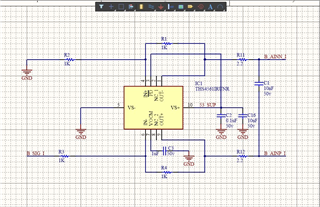

我正在尝试与 ADS8900定制板进行 SPI 通信、我的策略如下。

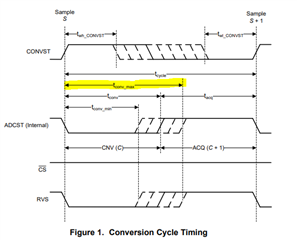

具有采样时钟的上升沿。 CONVST 引脚被拉低。

2.主机控制器/FPGA 监控 RVS 引脚的上升沿。

3.在 RVS 引脚上的上升沿、主机控制器将 CS 线路拉低、并向 ADS8900 SCLK 引脚提供22个串行时钟。

(基本图47区域1数据传输)

我的问题是我应该通过 SDO 引脚(比如我可以发送0x67A89)实际发送什么来收集 ADS8900 SDI3引脚中的20位样本? 数据表(第27页)中提供了一些数据、但我的陈述不清楚。

2.能否 使用单个 TPS7A4700 IC 为6 ADS8900B 供电?

此致

------

Pratik