你(们)好

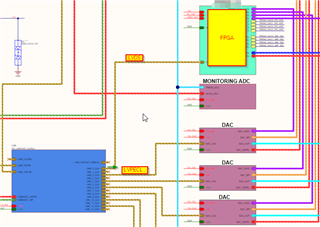

我们将在项目中使用 Dac3171 (7位接口版本),但遗憾的是,我们在使其正常运行方面遇到了一些问题。

基本上、我们在数据和 DAC 时钟上有警报、我们不知道问题可能是什么。

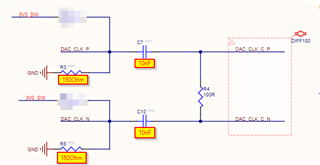

在数据时钟(LVDS)的下面, 信号直接来自 FPGA,不安装外部100欧姆电阻(使用内部 DAC 电阻)

DAC clk (LPECL20)下方的位置

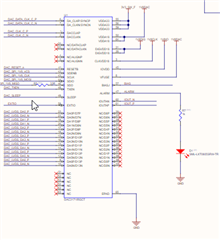

配置寄存器的下方

SetTxEn (false);

对于(uint32 lToggle = 0;lToggle < 100;lTog++)

SetReset (true)、mSlep (1)、SetReset (false)、mSlep (1);

//取消复位和难以实现的 TX

SetPowerDown (false);

SetSleep (false);

SetReset (false);

SetTxEn (真);

WriteConfig (CONFIG_00_REG、0x42FC);

SPIRead16 (CONFIG_06_REG 和 wData);=>读取0x4610 (数据表中的值为 Dac3171)

WriteConfig (CONFIG_01_REG、0x600E);

WriteConfig (CONFIG_02_REG、0x3F80);

WriteConfig (CONFIG_03_REG、0x0001);

WriteConfig (0x05、0x0000、true);

SPIRead16 (0x05、& wData);=>读取0xFFC0有时是0xFF40、0xFF80、即使我写入零来清除、我也总是读出警报

我可以通过 SPI 而不是 FPGA 设置输出电压。

有什么想法吗?