您好!

我们有一个具有 ADC12DJ3200 ADC 和 Xilinx Kintex Ultrascale FPGA 的定制板。 我们使用的是 JMODE 0。

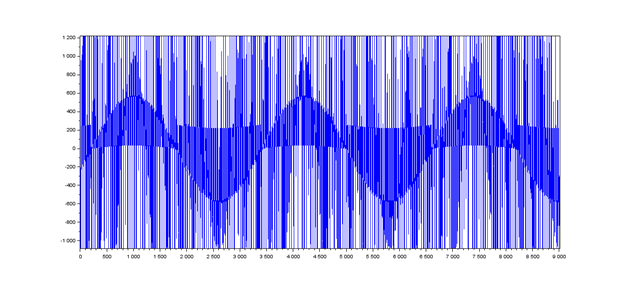

我将 KCU105参考设计用于 JMODE 0、但 FFT 不好。

因此、我测试了短传输测试模式、以检查传输层布局是否正确、但即使如此也不能正常工作。

在使用参考设计时、我不会期望传输层布置错误。 但我不知道我缺少什么。

采样频率为1600MHz、K=4、线路速率为6.4Gbps。

我已附上参考设计的 Slice 输出的屏幕截图(probe0至 probe19分别对应于 slice_21至 slice_40、而 probe20是240位传输层输出)。

期待您的支持。

谢谢。