主题中讨论的其他器件:ADS42JB49

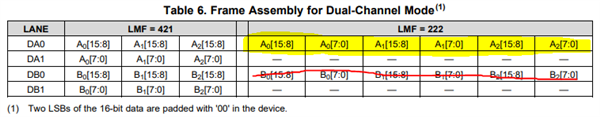

我正在 ILA 序列传输中读取 M 配置位输出1、根据表9、这意味着有2个转换器正在运行。 如何设置 M=1转换器? 我假设这是通过更改通道 A/B 是否断电来设置的。 我已将通道 B 断电、因此我假设 ADC 会在 ILA 中正确指示只有一个转换器。

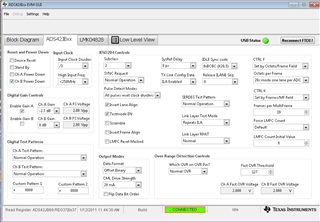

我所需的 LMFS 设置为1121。 我看到所有其他配置参数都在 ILA 中正确传输(L 除外、因为 M=1而不是0、它被配置为2个通道)。 我在下面附上了我的设置文件。

e2e.ti.com/.../ADS42JB49_5F00_EVM_5F00_ST_5F00_0810.cfg

尽管1121不是数据表中列出的配置、但基于以下讨论、它是有效的: e2e.ti.com/.../4073194