您好!

在菊花链模式下使用多个 DAC81404时,是否仍然可以执行读取操作(读回 DAC 的寄存器)?

链中最后一个 DAC 的 SDO 将连接回主机 MCU/FPGA。

如果可能,读取过程会是怎样的?

提前感谢您的帮助。

此致、

Marcel

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Marcel、您好!

在菊花链配置中、虽然共享芯片选择引脚保持低电平、但帧会通过链中的每个器件按顺序发送、直到芯片选择变为高电平、此时每个器件会锁存最后在 SDI 上接收到的命令。 通常、这意味 着主机 MCU 发出的第一个命令将被链中的最后一个器 件锁存、第二个命令将被第二个到最后一个器件锁存、等等。

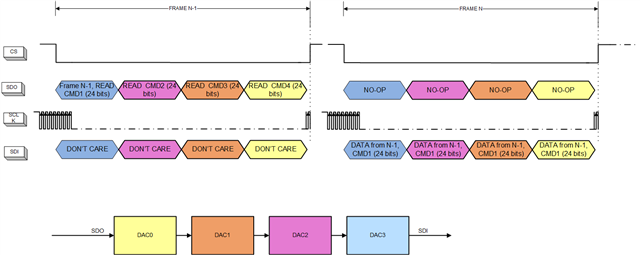

因此、假设您的菊花链中有4个 DAC、并且您希望从每个 DAC 中读取数据。 下面的时序图显示了如何完成此操作(请注意、此图是指 MCU 上的引脚、即图中的 SDI 线是微控制器的 SDI、连接到 DAC3的 SDO。)

从颜色编码中可以看出、在发送全部96位时、帧 N-1的前24位到达 DAC3、并且芯片选择 再次变为高电平。 这会在每个相应的 DAC 中锁存 READ_CMD 指令、当 MCU 通过拉低芯片选择再次启动通信时、DAC 将以其各自的数据进行响应、其连接顺序为相反顺序(因为 DAC3的输出首先到达 MCU、然后是 DAC2、DAC1、最后是 DAC0)。

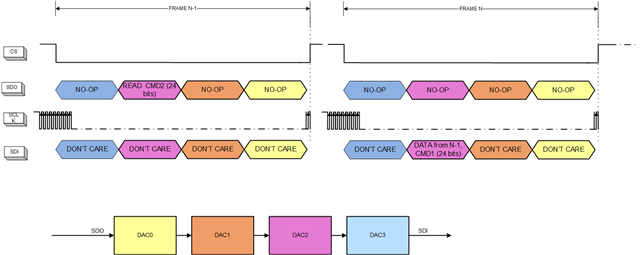

例如、如果您只需要来自 DAC2的数据、则时序图如下所示

因此、可以通过在正确的帧位置发出读取命令并适当地解析最后一个 DAC (MCU 的 SDI)的 SDO 中的数据来执行读取操作。

希望这对您有所帮助!

Anshuman