您好、E2E、

我知道、当 ADC 完成数据转换时、DRDY 引脚将切换为低电平。

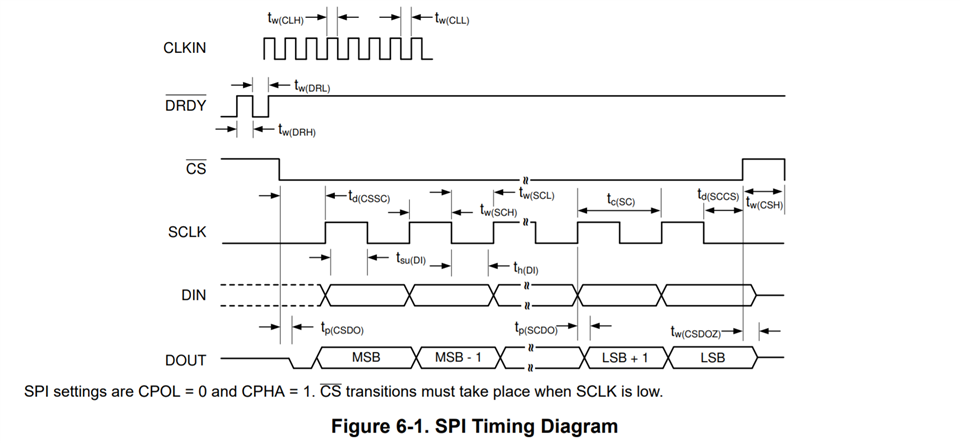

通常情况下、DRDY 被输入到 MCU 的中断触发器、然后与 ADC 进行 SPI 通信、但在我们的使用中、有另一个优先进程、启动 SPI 通信的时序会延迟、并且下一个 DRDY SPI 通信即使在时序上也可能不会结束。

我目前正在查看 OSR128和64 (TBM 位1)以及 OSR256。

当发生上述冲突时、DRDY 变为低电平的现象通常在 DRDY 变为低电平的一半时间内出现。

例如、如果 DRDY 在128us 周期内设置为低电平、则如果 DRDY 处于低电平的间隔恒定为128us->64us->128us->128us->128us、则呈波形。

此时 ADC 数据的锁存时序是多久?

此致、

ACGUY