主题中讨论的其他器件:THS4501、 THS4502、 THS4541、 THS4520、 THS4503

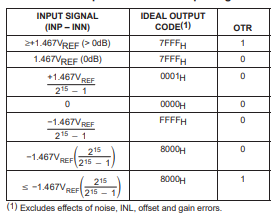

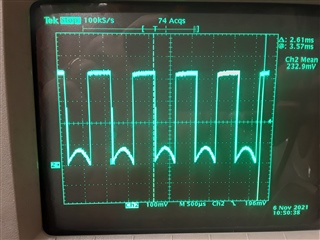

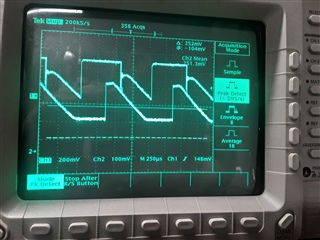

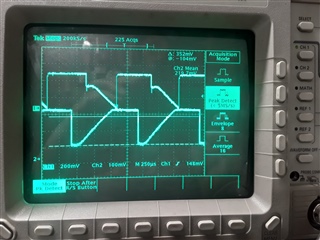

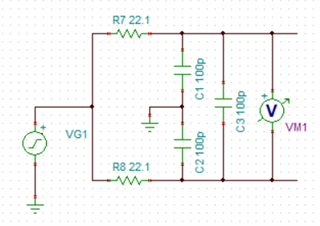

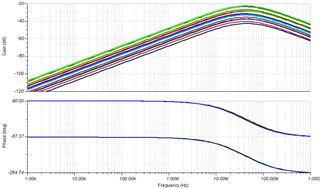

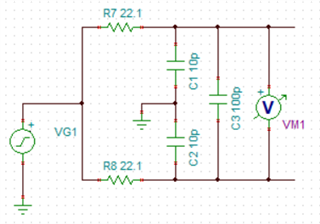

我在电路中使用参考设计建议、THS4501驱动 ADS1605。 对于任何低于 VMID 电平的信号电压、ADC 输出是正确的。 当输入电压超过 VMID 电平时、ADC 输出立即变为高电平、此时3个 MSB 的低电平位看起来运行正常。 我将输出转至 DAC、当输入低于 Vmid 基准时、DAC 上的波形是正确的、在高于 Vmid 基准时为满量程、这是我在3个 MSB 处于高电平时所期望的。 我无法理解导致这种行为的原因。 如果对寻找什么有任何帮助、我们将不胜感激。

谢谢、

霍华德