主题中讨论的其他器件: LMK04828、 LMX2592、 LMH5401、 ADC12DJ5200RF

您好、

ADC12DJ2700中的前景校准有问题。

通常、这意味着对于 JMODE_0、JMODE_2、前台校准通过。

此外、对于采样时钟为~2450及更高的 JMODE_16、将通过前台校准。

对于 JMODE_16、对于低采样时钟、主要在~2400MHz 和更低频率下、它会失败。

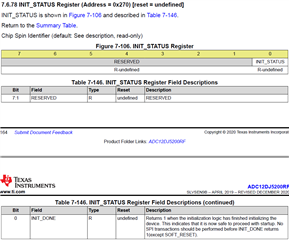

通常情况下、FG_DONE 位轮询花费高达400ms 的时间、直到检测到 FG 校准成功。

我们尝试将时间延长到几秒、但没有使用。 故障仍然存在。

在本例中、什么会影响 FG 校准故障?

我们应该如何进行调试?

背景信息:

在我们的设计中、LMK04828用作 JESD204B DEVCLK 和 SYSREF 的时钟分配器件、

它为 Xilinx FPGA (JESD204B 接收器)和 LMX2592供电、后者为 ADC12DJ2700采样时钟供电。

系统模拟输入进入 LMH5401差动运算放大器(SE 输入至差动输出)、该运算放大器馈入 ADC12DJ2700。

随附的查找 JMODE_16、2700MHz (FG 校准通过)和 JMODE_16、2200MHz (FG 校准失败)的 ADC 寄存器转储。

e2e.ti.com/.../AdcRegisterDump.txt

谢谢、

吉尔