请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADC3643 主题中讨论的其他器件:ADC3641、 ADC3683、 TSW1400EVM

您好!

我们计划在新项目中使用 ADC3641。 我下载 EVM 设计文件、发现它使用 FPGA 获取 ADC 结果、

1、为什么使用 FPGA?

2、我们可以使用 MCU 来获取它吗? 如果可以、设计时是否需要注意什么?

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Ronhua:

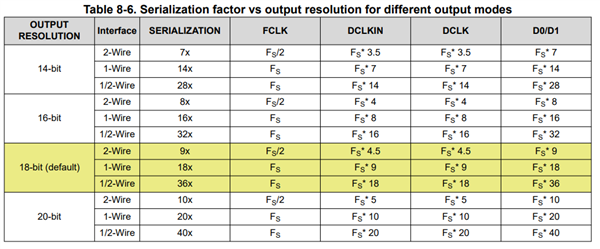

我们使用定制 FPGA 板(TSW1400EVM)接收 ADC 数据并在我们的许多 EVM 上生成 DAC 数据。 任何能够以产生的串行化速率接收 LVDS 数据信号的器件都非常适合使用、包括 MCU、DSP、FPGA 等 了解模式(1/2线制、1线制、2线制)和输出分辨率非常重要、这两种模式决定了产生的串行化速率是多少。 如需更多信息 、请参阅 ADC3683数据表第37页的表8-6。 不同输出模式下串行化因子与输出分辨率间的关系

此致、Chase