主题中讨论的其他器件: LMK04828、 DAC38RF80、 DAC38RF82

大家好、

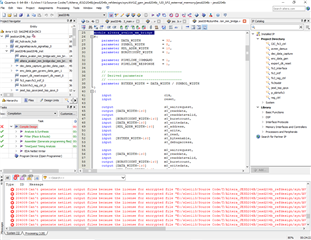

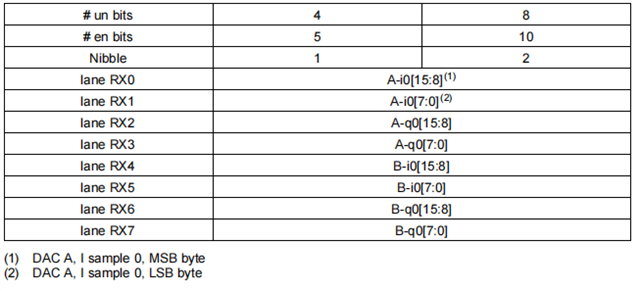

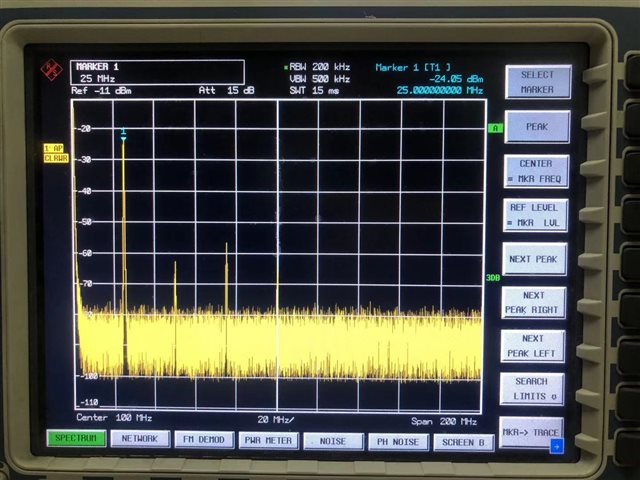

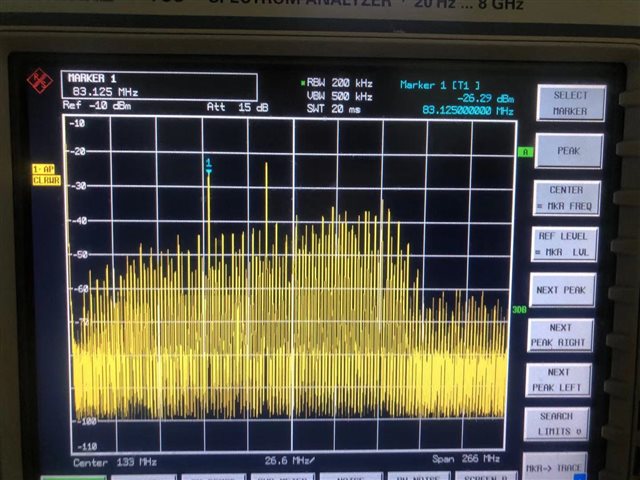

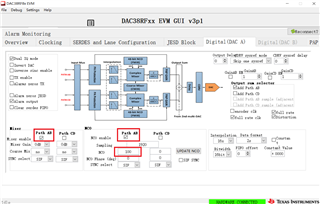

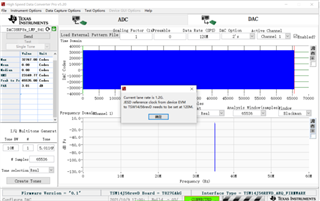

当 TSW14J56板连接到 DAC38RF80EVM 以进行调试、外部时钟和 DAC_ PLL 模式时、可以根据 文档中设置的参数(6144MHz)生成波形、但对于外部时钟模式、当6144MHZ 时钟发生变化时、无法生成波形、 软件报告以下错误。

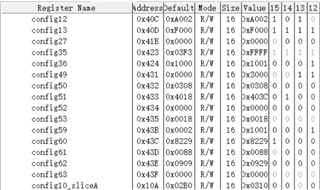

看看该误差、应该是因为在射频采样率发生变化后、也需要更改 JESD 的基准时钟。 但是、在软件中无法更改时钟。 如何调节此处的 JESD 参考时钟?

此致、

罗美