主题中讨论的其他器件: TPS54319、 LMK04828

大家好、

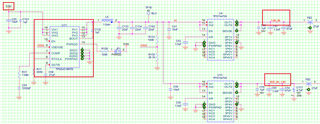

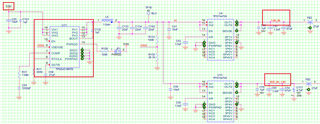

ADS42JB69EVM 设计中的"电源"页面显示、它 使用"TPS54319"模块将"5VIN"直流电压转换为"4V"、然后使用"TPS7A4700"模块将"4V"更改为"1.8V"(图1)。

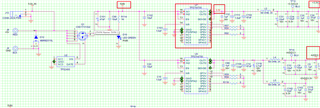

我的问题是、为什么不在同一页中使用"TPS7A4700"或"TPS54319"直接将"5V"更改为"1.8V"(如"5V- 3.3V")(图2)。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

ADS42JB69EVM 设计中的"电源"页面显示、它 使用"TPS54319"模块将"5VIN"直流电压转换为"4V"、然后使用"TPS7A4700"模块将"4V"更改为"1.8V"(图1)。

我的问题是、为什么不在同一页中使用"TPS7A4700"或"TPS54319"直接将"5V"更改为"1.8V"(如"5V- 3.3V")(图2)。

您好、Jim、

我想问另一个有关您的设计的问题、

关于 JESD204B 子类1、嗯、、SYSREF、

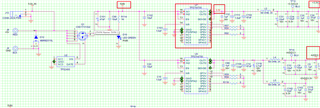

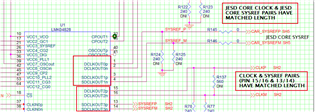

我已经看到您在设计中标记了"JESD 内核时钟和 JESD 内核 SYSREF 对具有匹配的长度"(第3页 LMK04828)、我知道它具有相同的长度。

那么、我的问题是、为什么不将所有时钟输出线路设置为 ADC 和 FPGA 时钟的长度相等(如下图所示)?

此致、

非

NaN、

只有 CLK 和 SYSREF 必须在 ADC 和 DAC 之间匹配长度、对于 FPGA、这些长度可能不同、但 CLK 和 SYSREF 必须匹配进入 FPGA 的长度。 请参见随附的。

此致、

Jim