问题:

将 HR 引脚连接至低电平时、将 EXT 引脚外部电阻从120K 转换为60.4K 时、即在将 VLP 模式切换为 LP 模式时、功耗确实会更高、但 ADC 的输出噪声不会得到改善。

但此时、AFE 前端等效自噪声和 ADC 的理论输出噪声基本相等、因此在开关模式后、总体等效自噪声输出应有所降低。

客户想知道原因是什么。 谢谢!

此致、

樱桃周

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Cherry、

将 REXT 从120k 切换到60k 对 ADC 中的总噪声影响很小。 它确实会略微降低内部放大器中的噪声、但来自其他内部组件的热噪声决定了总 ADC 噪声。 增加功率(减少 REXT)的目的是支持更高的输入时钟频率和更高的输出数据速率。 减少 REXT 会增加内部放大器带宽、从而缩短支持更高输出数据速率所需的稳定时间。

VLP 模式下的最大 Fclk 为4.4MHz。 将 REXT 降低至60.4k (增加总功率)可使 Fclk 增加至8.8MHz。 对于相同的 OSR 设置、您现在可以以2倍的输出数据速率运行。

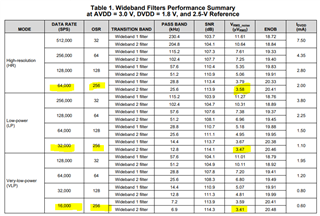

数据表中的表1确认了不同功率模式下的噪声不会发生变化;它主要取决于 OSR 设置。 例如、OSR=256、WB2滤波器、在所有情况下、噪声大约等于3.5uVrms (随着 Fclk 的增加、会有一些变化)。

此致、

Keith Nicholas

精密 ADC 应用

您好、Cherry、

1. 是的、正确。 对于相同的 FCLK、OSR 和滤波器设置、使用不同模式时、ADS127L01的内部噪声不会改善。 在较低频率下运行 Fclk 确实会让外部基准和放大器有更多的时间稳定下来、因此它可能会改善外部组件导致的总体噪声、但不会改善 ADC 的噪声。

2. 是的、ADS127L01的最低噪声是使用最高 OSR 设置时的噪声。 例如、使用宽带滤波器2和64ksps 的输出数据速率、您可以在 OSR=256且 Fclk=16.384MHz (SNR =113.9dB)的 HR 模式下运行、也可以在 OSR=64且 Fclk=4.096MHz (SNR =108.3dB)的 VLP 模式下运行。

此致、

Keith