Other Parts Discussed in Thread: DDC114

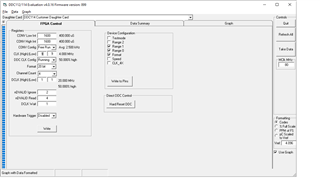

我尝试在 EVK FPGA 固件中使用与 我们的微控制器在驱动 DDC114时执行的代码中相同的设置、以检查我们是否获得相同的采样值和噪声。 但是、我很难将 GUI 设置与我们的代码相关联。 用户指南

我们的微代码将积分时间设置为超时、翻转 CONV 位、该时间以纳秒为单位。 然后、DDC 集成、当得到结果时、DVALID 变为真。

为了使用 FPGA GUI 来执行 DDC、我需要设置寄存器组、但很难分辨是什么除以什么才能在正确的位置获得数字...

MCLK 是否被分频为 CLK、而这又被分频为 CONV?

至于除数、

时钟 MCLK 除以 CLK 高电平+ 1 + CLK 低电平+1中给出的周期数、以产生 CLK 吗? 因此、80MHz 的 MCLK、如 UI 中所述、除以9和9实际上除以20、得到4MHz?

4MHz 的导出 CLK 提供周期为250nSecs 的分频器输出。 除以1600个250nS 周期(即1600个低 INT 和1600个高 INT)可得到400uS 低电平、而对于高电平也是如此-这相当于800uS 的集成时间吗?