您好!

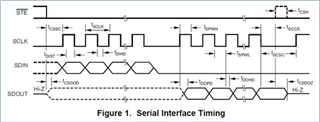

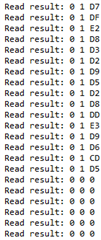

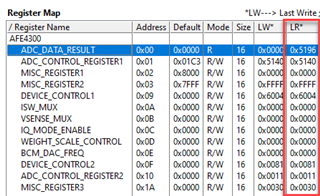

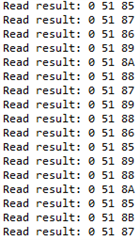

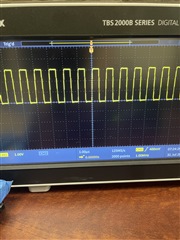

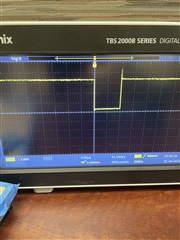

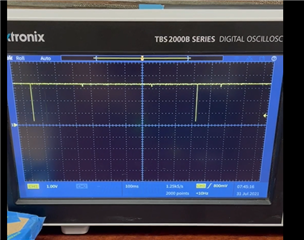

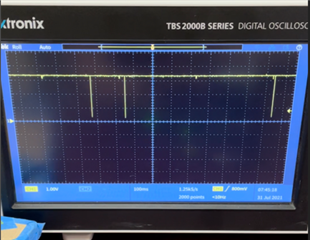

我尝试使用评估模块的 SPI 接口将 AFE4300EVM 连接到 nRF5284-DK。 通过从 AFE4300EVM 上拆下 MMB3板并将 J103的引脚连接到 nRF52840开发套件的正确 GPIO、我可以将两个板连接在一起。 我能够写入 AFE4300的寄存器、该寄存器在启用体重秤链后通过检查 VLDO 的电压进行了测试。 但是、当尝试从任何寄存器读取数据时、我会遇到一个问题、包括 ADC_DATA_register。 RDY 信号以高电平状态开始、当每个寄存器被写入时脉冲为低电平8微秒、最后保持高电平/在写入寄存器后不会中断。

我的问题是:

1) 1)为何 RDY 信号开始为高电平、而数据表的图10和11指示 RDY 应开始为低电平?

2) 2)我应该在写入寄存器时还是仅在读取时监视 RDY 信号?

3) 3)如果 RDY 的短暂低电平脉冲表示转换结束、那么我应该准备好在最后一次寄存器写入后立即读取数据、还是可以防止立即发生中断/数据转换?

4) 4)如果 AFE4300是串行总线上的唯一从设备、STE 是否有任何用途?