主题中讨论的其他器件: ADS1120、 ADS112C04

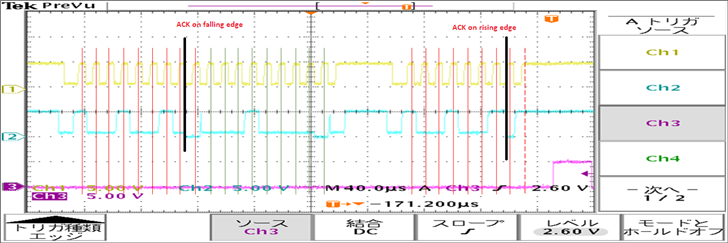

黄色 SCL

蓝色 SDA

情况

只有从器件(ADS 1119地址为0×49)和主器件侧总线缓冲器(P 82 B 96 TD)连接到总线。

执行 ReadData 时执行了以下操作。

如示波器的波形所示、从 IC 在8CLK 时返回 ACK。

问题

・从 IC (ADS 1119)为什么在8CLK 时返回 ACK?

・是否有解决方案?

谢谢、此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

黄色 SCL

蓝色 SDA

情况

只有从器件(ADS 1119地址为0×49)和主器件侧总线缓冲器(P 82 B 96 TD)连接到总线。

执行 ReadData 时执行了以下操作。

如示波器的波形所示、从 IC 在8CLK 时返回 ACK。

问题

・从 IC (ADS 1119)为什么在8CLK 时返回 ACK?

・是否有解决方案?

谢谢、此致、

您好、Kazuya、

通信来自微控制器。 在36的 ADS1119数据表中显示了 RDATA 命令结构。 从示波器图中可以看出、写入 RDATA 命令的通信按预期工作、但数据读取从未完成、因为最后一位设置为低电平(器件写入)而不是高电平(器件读取)、因此对器件进行错误寻址。

通信结构依次为开始、器件地址+写入(+ ACK)、RDATA 命令(+ ACK)和重复开始、然后是器件地址+读取(+ ACK)。 但是,ADS1120看到重复的“Start (开始)”后跟一个设备地址+写入,而不是一个读操作,这是与格式有关的不正确通信。

因此、将通信更正为正确的格式应该可以解决该问题。

此致、

Bob B

您好、Kazuya、

I2C 总线上是否还有其他器件? 每次尝试从 ADS1119读取时是否会看到相同的响应? 写入和读取寄存器是否会出现任何问题?

如果 ADS1119将 SDA 拉低、 那么示波器上可能会有一个未捕获的 SCL 小毛刺脉冲。 您是否有可共享的原理图? I2C 总线上拉电阻的值是多少? 微控制器和 ADS1119之间是否使用了长导线?

此致、

Bob B

你(们)好 Bob

除了 I2C 总线、主器件侧只有一个总线缓冲器。

使用的是 RDATA 的20ms 轮询、错误频率为每天1或2次。

当读取和写入寄存器时、WREG 被用于初始设置、但是没有问题。 未使用 RREG。 RDATA 期间发生错误。

I2C 总线的上拉电阻为2.2 kΩ。

Micro 和 ADS 1119之间的导线约为100 mm 至200 mm。

我们已确认数据表中的信号完整性和时序是正确的。

因此、我认为在硬件方面没有问题。

最好的地方

您好、Kazuya、

即使是100至200mm 的短线也可用作天线、以在环境中拾取 EMI/RFI。 因此、即使设计本身相对于通信时序而言是正确的、SCL 上拾取的任何噪声也可以视为转换。 完全移除电线并使用 PCB 迹线连接、或者至少尽可能缩短电线长度、将会有所帮助。

此外、导线本身也会给总线增加很大的电容。 您可以尝试进一步减小上拉电阻、看看这是否有用。 ADS1119和微控制器之间的接地连接也很重要。 这应该是一个低阻抗连接。

此致、

Bob B

您好、Kazuya、

ADS1119和 ADS112C04共用同一个数字接口。 ADS1119确实遵循 I2C 通信协议并支持标准、快速和快速+模式。 数据表第6.6节给出了 I2C 时序要求。 该测试使用10pF 和400pF 之间的总线电容。 上拉电阻为1k。 使用电线连接将增加总线电容。 将上拉电阻器更改为1k 也可以改善通信。

如果我们返回并查看您提供的通信的原始示波器截图、我们将看到:

此时外设似乎未完全完成通信。 通常情况下、ACK 从第8个 SCL 的下降沿开始、并通过第9个时钟保持低电平。 请注意、在差异点、转换似乎发生在第8个 SCL 的上升沿而不是下降沿。 在这里、我怀疑发生的干扰足够小、不能显示在示波器图上、但也足够长、可以在 ADS1119上注册为时钟脉冲。

如果存在通信错误、则固件中应存在错误处理例程。 您不能假定通信始终按预期工作。 在示波器屏幕截图中、通信似乎从未实际完成。 可能没有、只是没有显示。 但我曾看到过与 I2C 通信时没有错误处理例程或总线错误的情况、其中总线将挂起并需要复位。

另一个要尝试的操作是在写入和读取之间发出重复的 Start 而不是 Stop 和 Start。

此致、

Bob B

你(们)好 Bob

这是否意味着 ACK 通常在第8个 SCL 的下降沿启动、但由于小毛刺脉冲而被识别为时钟?

如果一个小毛刺被识别为一个单时钟脉冲、ACK 是否发生在下降沿而不是上升沿?

当错误发生时、为什么在上升沿发生 ACK、通常在下降沿发生?

我正在尝试使用更精确的示波器进行确认、但 ADS 1119在多 Hz 时会将其识别为时钟脉冲? 此外、当我使用示波器进行检查时、应该观察哪个时序?

此致

您好、Kazuya、

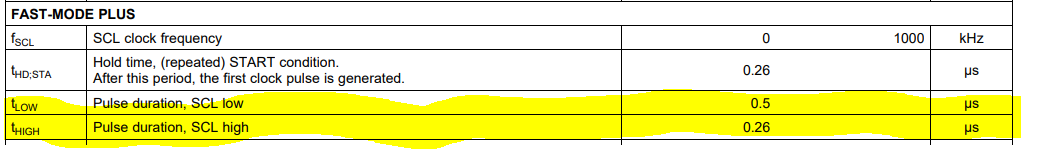

我相信您的图基本上准确地表示了正在发生的情况、除了在错误状态下、第8个时钟下降沿将使 SDA 恢复为高电平、微控制器将在第9个时钟处看到 NACK。 在正常情况下、SDA 在第9个 SCL 的下降沿返回高电平、该下降沿发出 ACK 信号。 ADS1119将干扰作为时钟进行查看。 数据表显示了 FAST+的以下信息:

如果时钟边沿上有一个轻微的振铃或瞬态电平持续500ns、ADS1119会将其视为有效时钟。 考虑到噪声可以在接线上拾取、或者可能存在某种形式的接地反弹、这也可能是一个因素。 如果您通过导线连接到 ADS1119、那么微控制器和 ADS1119之间的 DVDD 和 GND 是如何连接的?

SCL 的逻辑低电平为0.3*DVDD。 如果 ADS1119的 DVDD 为5V、则逻辑低电平为1.5V 或更低。 被视为逻辑低电平的毛刺脉冲只需在 SCL 上达到1.5V。

让我们考虑一下、这种干扰正在发生、并且已经做出了所有可能的改进。 问题仍然在于固件如何处理 NACK? 您不能始终拥有完美的通信。 您可能会在收到 NACK 时发生事件。

您的代码中应实现如下所示的内容:

此致、

Bob B