在 ADS1675的数据表中、第1页说明的第二段显示宽带路径具有86dB 的阻带衰减。 这也列在第3页的数据表 的数字滤波器特性(宽带宽路径)下 、阻带衰减= 86dB。

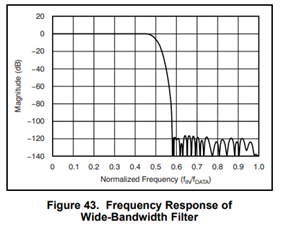

在第21页、图43似乎显示了频率响应的阻带大约为115dB。

当滤波器响应看起来为115dB 时、您能否解释86dB 的来源?

更令人困惑的是、修订历史记录显示、在数据表的前一修订版中、86dB 曾经是115dB。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

在 ADS1675的数据表中、第1页说明的第二段显示宽带路径具有86dB 的阻带衰减。 这也列在第3页的数据表 的数字滤波器特性(宽带宽路径)下 、阻带衰减= 86dB。

在第21页、图43似乎显示了频率响应的阻带大约为115dB。

当滤波器响应看起来为115dB 时、您能否解释86dB 的来源?

更令人困惑的是、修订历史记录显示、在数据表的前一修订版中、86dB 曾经是115dB。

您好、Michael、

首先、欢迎访问 TI E2E 社区。

图43准确地显示了数字滤波器响应、并在阻带中反映出115dB 的衰减。

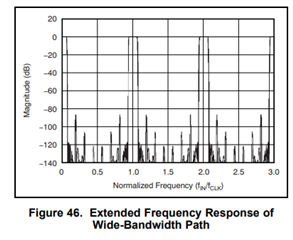

但是,对于带外频率(大于1/2*数据速率),有些区域会发生互调,从而产生超过数字滤波器阻带衰减的响应峰值。 数据表的图46中显示了这些参数。 最坏情况下的区域为86dB、不包括频率为调制器频率倍数的通带区域。

当与 ADC 输入上的抗混叠滤波器配合使用时、阻带衰减得到改善。

此致、

Keith Nicholas

精密 ADC 应用

您好、Michael、

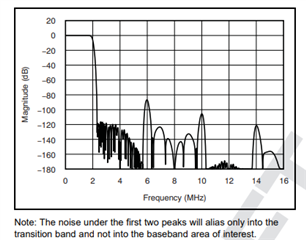

我做了更多的挖掘。 对于 ADS1675、这是数字滤波器的实际响应、而不是互调失真。 阻带中的这些峰值将混叠到转换区域而不是通带、因此假设这些混叠信号不会干扰任何相关的通带信号。

在任何情况下、如果 OSR=32、峰值都将相对于图46按比例缩放、图46使用 OSR=8。 当 OSR=32时、第一个峰值将为1.5MHz、第二个峰值为2.5MHz。 下面是我在 OSR=8时发现的另一个图;当使用 OSR=32时、只需将 x 轴除以4即可。 该图假设时钟频率设置为32MHz。

如果您担心转换区域中存在混叠信号、那么您的抗混叠滤波器可设计为根据您放置转角频率和滤波器阶数的位置进一步将这些信号降低几 dB。

此致、

Keith