主题中讨论的其他器件: TSW14J10EVM、 LMK04828

您好!

我们已订购评估板 DAC39J82EVM 并已开始特性评估。

我们正在尝试在实验室中测量 NSD、但由于设备限制、我们无法满足这些数字。

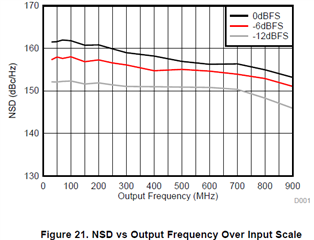

由于这是我们设计中的一个重要参数、我们想知道用于验证 DAC 数据表(图21、第21页)中提到的 NSD 数字的测量设置。 您能否提供所 用的测量设置和参数? 数据表中的 NSD 数字附在下面以供参考

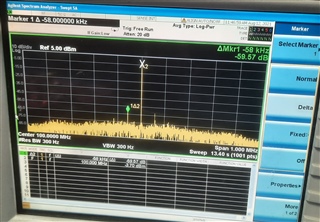

DAC39J82EVM 的另一个观察结果是 、当从 DAC 生成任何输出时、 在生成输出的两侧以大约58-60 KHz 的偏移频率观察到杂散分量。 即使将 DAC 配置为仅生成 LO 输出(FPGA 板断电且 DAC 生成 LO @ 100MHz)、也能看到这些杂散分量。 您是否了解这些杂散组件以及如何消除它们? 下面随附了参考快照。

谢谢、

Kiran