大家好、

我们正在项目之一中使用 ADS124S08 IC。 我们面临着芯片选择(CS)引脚的一些通信问题。 当我们直接将 CS 引脚连接到 DGND (意味着我们使用外部跳线将 CS 引脚连接到 DGND)时、IC 工作正常、我们能够正确读取所有12个通道(单端)。

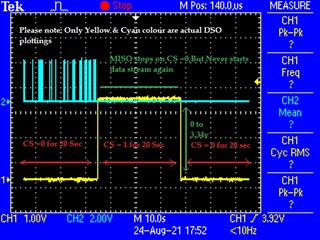

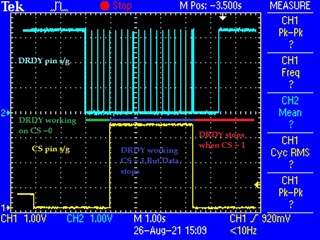

我们使用 Raspberry PI 计算模块(CM-4)与 ADS124S08进行通信。 当我们将 CS 引脚(ADC 的)连接到 CM-4芯片选择引脚时、我们无法获得正确的读数(显示0-2mV 的垃圾值)、其中 AIN 引脚上的实际输入信号为0.5V-2V。增益设置为1。

在我们的项目中、我们使用了两个 ADS124S08、如果我们强制先将一个 ADC IC 接地、并使用跳线 J1=Closed & J2=open (附加原理图)、则第一个 IC 工作正常、但另一个 IC 处于非活动状态、反之亦然。 我们的目标是从两个 ADC IC 获取读数、只有在我们能够从 GPIO 引脚控制/切换 CS 引脚(而不是通过物理接地)的情况下才能实现。

在获取垃圾数据时,我们甚至尝试了将 Reset to ADC (重置到 ADC)(通过将 RESET 引脚接地),但我们仍然得到错误的数据。 在我们为整个器件(CS 引脚接地)供电之前、重新启动器件。

我们尝试的操作如下。

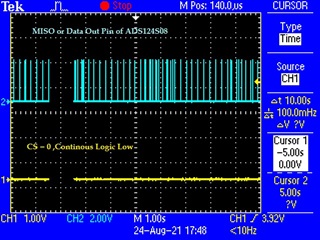

答:我们检查数字示波器 CS 引脚上的信号、当信号为低电平时、它提供适当的0V、而在高电平时、它是3.3V。

b.我们尝试通过 CM-4模块上的其他可用 GPIO 引脚提供 CS 信号。

c.将下拉电阻器10k 和4.7K (一次一个)连接到 CS 引脚。

d.尝试使用 NPN 晶体管(BC847)控制 CS 引脚。

我们是否缺少任何寄存器读取/写入、读取序列、时序或任何硬件点等

请建议。 提前感谢