您好!

感谢您的耐心等待

请找到所附的波形

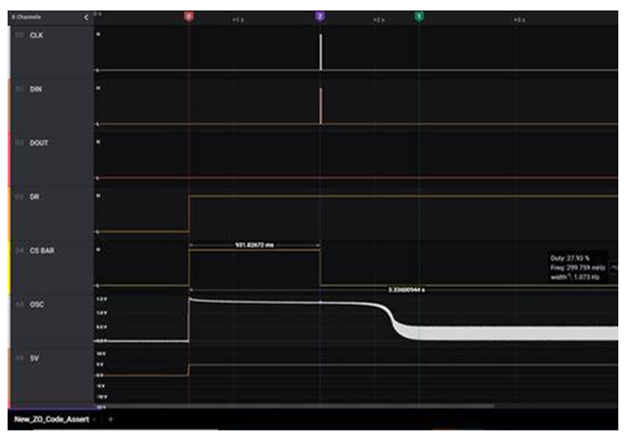

当 CS 在晶振稳定之前变为低电平时、ADC 抛出错误(DOUT 即将到来)。 请找到所附的波形。 在这里、CS 时间为715ms

我们已将 CS 时间增加到936ms。 但是、当我们调整 CS 引脚时序时、振荡器时间也会在 不修改硬件的情况下得到延长。 请告诉我们原因。

在这种情况下、ADC 也会抛出错误。 这个问题是随机出现的。 如果晶体在 CS 变为低电平之前稳定下来、则该误差未出现在图片中。

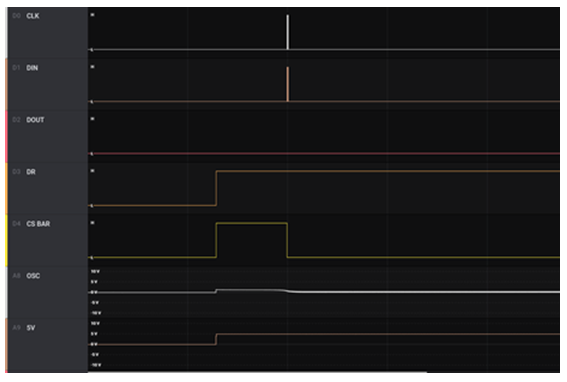

无错误情形:

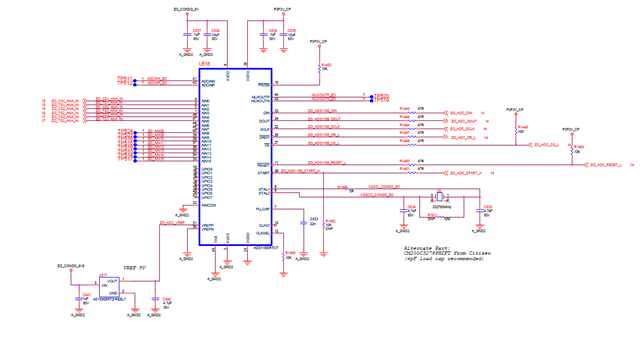

原理图:

此致、

Murugavel.S