请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADS7038Q1EVM-PDK 主题中讨论的其他器件:LAUNCHXL-F28379D、 ADS7038

您好!

我们购买了 ADS7038Q1EVM-PDK 评估板。 我从 PAMboard 中移除了包含 ADC IC 的子板、并将其直接连接到 LAUNCHXL-F28379D 板。

我的 LP 程序表面上是使用 SPIB 以500kbps 的速率与 ADC 进行通信、我 能够在 AIN0上获取合理的样本。 但是,我担心计时方案只能勉强工作,并且不能全速运行,因此我想确保 F2837xD (主)计时方案也是纸上的正确计时方案。

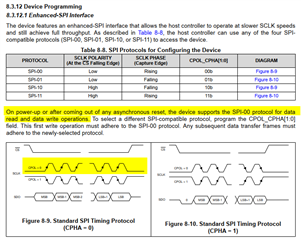

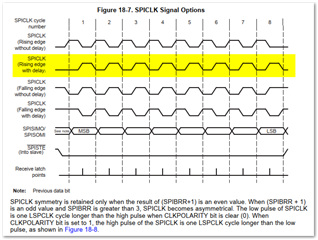

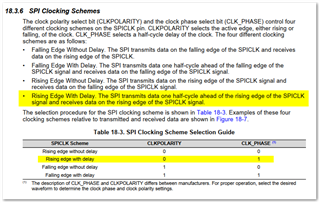

ADS7038 (从器件)的默认时钟方案为 SPI-00 (CPOL = 0且 CPHA = 0)。 在比较 ADC 和微控制器的时序图后、我得出结论:F2837xD 中正确的时钟方案是“有延迟的上升沿”(POL=0、PHA = 1),是不是这样吗?

ADS7038:

F2837xD 手册:

非常感谢。