主题中讨论的其他器件:LMK04828、 DAC38J84

您好!

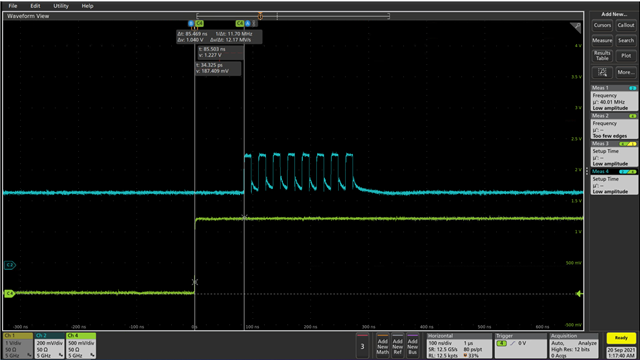

我使用 SYS_SYNC 信号来启用 DAC 输出。 在 SYS_SYNC 信号的上升沿到达 LMK04828的 SYNC 之后, SDCLKout*上有输出。

我可以捕获 SDCLKout*,但 SYS_SYNC 和 SDCLKout*之间的延迟。

我的系统设置详细信息如下所示:

输入1上有100MHz 输入。

2、DAC 数据速率为400MSPS、我使用2作为内插。

您能给我一些关于如何配置 LMK04828和 DAC38j84的建议吗? 谢谢!