主题中讨论的其他器件: LMK04828

尊敬的所有人:

我正在努力解决 DAC39J84的配置问题。

由于通道上的错误、我没有看到 DAC 的任何输出。 即使我能够 执行 NCO 测试并且 PRBS 测试模式成功。 我想问您是否可以检查 DAC 的配置。

这是我的配置:

- 来自 Abaco DAC39J84和 LMK04828的 FMC120

- 带 TE0808的 Trenz 板、带9EG。

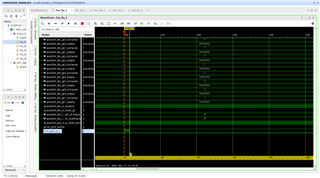

在 FPGA 端、我签署了 IP Xilinx JESD204b (PG066)和 IP JESD204 PHY (PG198)。

我将通过 I2C 至 SPI 桥与 DAC 通信。

下面介绍了 LMK 如何连接到 DAC 和 FPGA,以及预期的频率是多少 :

LMK 100MHz CLK2in 输入时电路板的内部基准

DCLK0→1000MHz DAC 时钟

设计中的 DCLK2→250MHz 时钟打开以进行调试

DCLK4→1000MHz ADC A 时钟

DCLK6→1000MHz ADC B 时钟

连接到 GTH 线路的 DCLK8→250MHz 时钟

连接到 GTH 线路的 DCLK10→250MHz 时钟

配置寄存器的设置与文件 lmk04828.txt 中的设置相同。

e2e.ti.com/.../1830.lmk04828.txt

由于可以看到配置形式、我将 SYS REF 编程为间隙脉冲。

对于 DAC、这些是主要参数:

L = 8

M = 4

f = 1

S = 1

HD = 1

Fdac = 1000MHz

DACPLL 使能、VCO L 频带 P=4、M=2、N=2

JESD 时钟分频器2

串行器/解串器:10Gbps、全速率、PLL @ 2.5GHz、SerDes_REFCLK_div=2、MPY =0b10100

此处是编程序列

|

操作读/写 |

地址 |

值 |

注释 |

|

HW DAC_RESET |

(应用此复位后、DAC sif 寄存器具有默认值、因此此硬件复位有效) |

||

|

写入 |

0x02 |

0x0082 |

|

|

主机 IRQ |

0x7f |

0x800a |

从数据表中、从该寄存器读取的 visionid=0x1为0x2 |

|

写入 |

0x1A |

0x0 |

|

|

写入 |

0x0 |

0x18 |

|

|

写入 |

0x25 |

0x2000 |

JESDCLK_DIV |

|

写入 |

0x31 |

0x6C08 |

|

|

写入 |

0x32 |

0x120 |

|

|

写入 |

0x33 |

0xAF40 |

|

|

写入 |

0x3B |

0x8800 |

|

|

写入 |

0x3C |

0x828 |

|

|

写入 |

0x3D |

0x8E |

|

|

写入 |

0x3E |

0x108 |

|

|

写入 |

0x3F |

0x0 |

|

|

写入 |

0x46 |

0x44 |

|

|

写入 |

0x47 |

0x190A |

|

|

写入 |

0x48 |

0x31C3 |

|

|

写入 |

0x49 |

0x0 |

|

|

写入 |

0x04 |

0xFF |

报警屏蔽 |

|

写入 |

0x05 |

0xC0F2 |

报警屏蔽 |

|

写入 |

0x06 |

0xFF00 |

报警屏蔽 |

|

写入 |

0x24 |

0x10 |

SYSREFMODE_for_clkdvr |

|

写入 |

0x1E |

0x2222 |

SET_SYSREF_for_DSP |

|

写入 |

0x1f |

0x2220 |

SET_SYSREF_for_DSP |

|

写入 |

0x20 |

0x2022 |

SET_SYSREF_for_DSP |

|

写入 |

0x23 |

0x2022 |

SET_SYSREF_for_DSP |

|

写入 |

0x5C |

0x1111 |

SYSREFMODE_OR_JESD |

|

写入 |

0x34 |

0x80 |

SYNC 设置 LVDS 格式 |

|

写入 |

0x4B |

0x1F00 |

Buffer=32帧=1、每帧八位位组=1 |

|

写入 |

0x4C |

0x1F07 |

K=32、L=8 |

|

写入 |

0x4D |

0x0300 |

M = 3 S = 1 |

|

写入 |

0x4E |

0xF4F |

SCR=0、高密度、N=16 N'=16 |

|

写入 |

0x4F |

0x1CC1 |

|

|

写入 |

0x51 |

0xFF |

|

|

写入 |

0x52 |

0xFF |

|

|

写入 |

0x54 |

0xFF |

|

|

写入 |

0x55 |

0xFF |

|

|

写入 |

0x5F |

0x123 |

|

|

写入 |

0x60 |

0x4567 |

|

|

写入 |

0x01 |

0x0000 |

|

|

写入 |

0x03 |

0xA300 |

|

|

写入 |

0x61 |

0x211 |

|

|

DAC_TX_EN |

|||

|

写入 |

0x4A |

0xFF1E |

|

|

写入 |

0x4A |

0xFF1F |

|

|

写入 |

0x4A |

0xFF01 |

|

|

在 LMK04824上启用1个脉冲 |

|||

|

清除 CONFIG100-CONFIG107 (先写入全部1、然后写入全部零) |

|||

|

通道状态寄存器 CONFIG100-CONFIG107提供0x400 |

|||

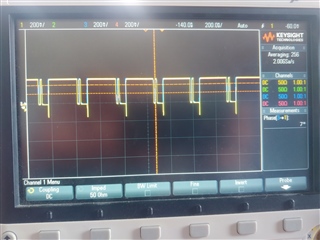

因此、我们有一个"代码同步错误"、 DAC 输出中没有任何内容。

在 DAC 编程序列之后、我可以看到同步信号在 切换后保持高电平。

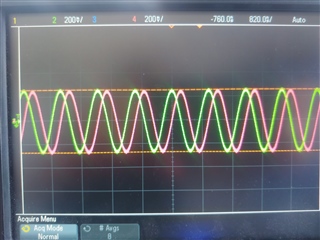

为了查看我是否可以从 DAC 获取输出和从 LMK 获取 SYSREF、我尝试执行 NCO 测试、并且在我从 SIF 配置输出电平后、混频器频率并发送 SYSREF 脉冲、我可以获取我期望的正弦波。

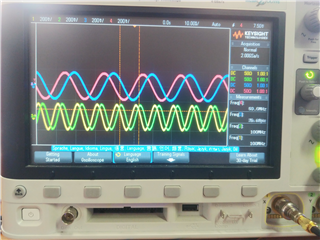

我执行的另一项测试是 PRBS 测试、方法是从 FPGA 发送 PRBS 序列、并通过期望相同的 PRBS 或不同的 PRBS 来配置 DAC 通道。

当 DAC 需要扩散序列时、Alarm 引脚变为高电平、 当 PRBS 序列正确时、它保持低电平。 从这些测试来看、SERDES 链路似乎没有任何问题。

我还会执行链路层测试(关于这些测试、我对编程序列并不完全确定):

ILA 测试 来自 conf100-107 I 获取始终为0x400

K28.5测试:conf100-107 I obtain always 0x0

D21.5测试:conf100-107 I obatin Always 0x0

因此、很明显、代码同步错误 似乎是问题所在。

您对我如何解决此问题有什么建议吗?

感谢您的关注