请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

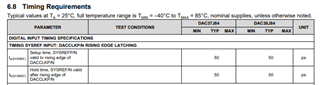

器件型号:DAC38J84EVM 在 PLL 禁用模式下、DACCLK 直接从引脚使用、SYSREF 需要尊重设置和保持时间。

在评估板上、LMK 可以为器件时钟生成高达2.457GHz 的频率、并将分频器设置为0。 但是、这是否会导致问题、以确保 Tsu 和 TH 得到尊重、因为最小模拟延迟为150ps? (设备时钟的半周期为203ps,因此如果我们使用延迟来满足保持时间,我们可能会遇到设置冲突?)

如果我使用 PLL、那么我可以使用较低的 DACCLK 频率、并确信 SYSREF 在引脚输入处满足时序要求。 然而,由于 PLL 将乘以 DACCLK,SYSREF 是否仍能满足芯片内部的时间限制? 我是否必须担心这个问题、或者仅仅尊重引脚输入上的 Tsu 和 TH 就足够了?

谢谢。