主题中讨论的其他器件: ADS122U04

员工、

我们实施了 ADS122C04。 AVDD 和 DVDD 的电源稳定几分钟。 我们对 RESET 引脚进行脉冲、并在上升沿之后~4us 开始写入 I2C 总线。

根据数据表、这应该起作用:

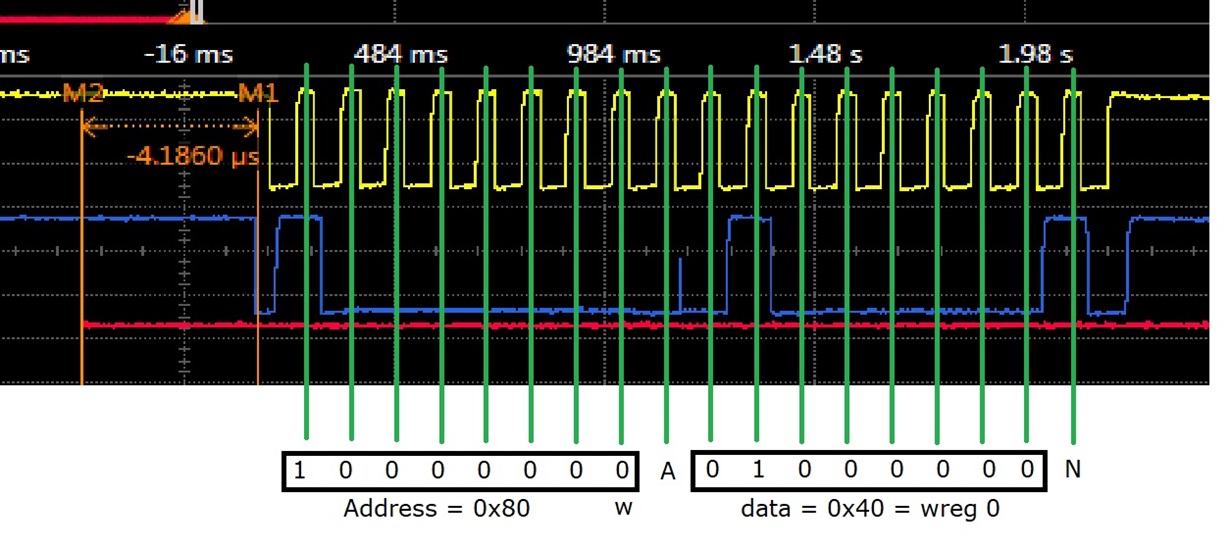

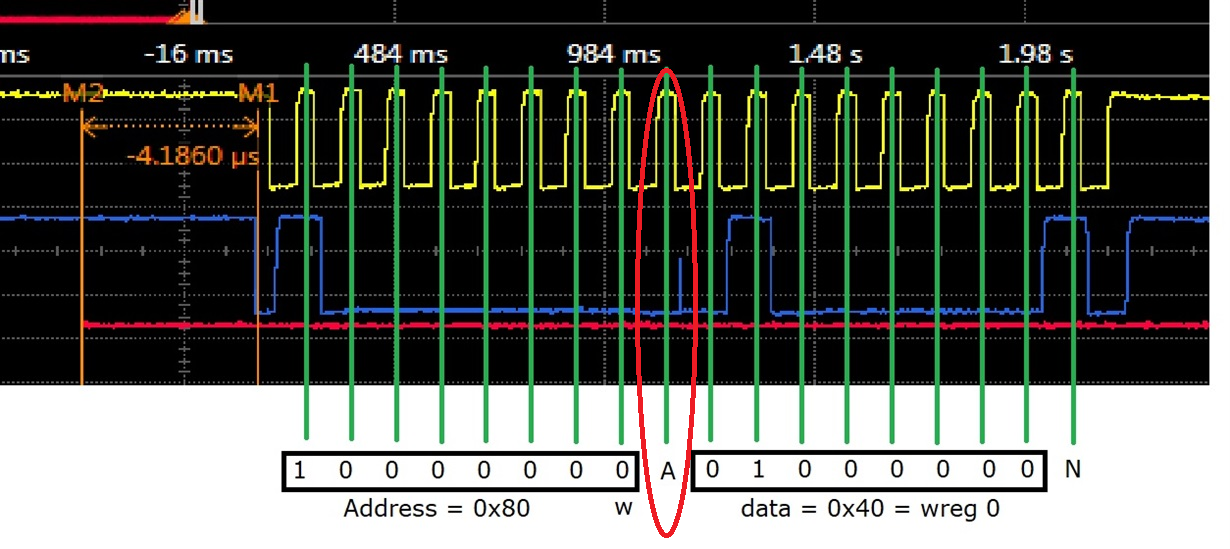

但当写入寄存器指针时、我们将得到 NACK。 例如、下面是一个示例示例示例示例、其中写入器件地址0x40h (7位寻址)和寄存器0x40h (WREG)。

通过稍微放大、我们可以看到以下内容:

这与数据表的第8.5.3.7节匹配:

将等待时间增加到25us 以上似乎解决了这个问题。

我们怀疑所需的延迟接近数据表中指定的超时周期。 在正常时钟模式(256kHz)下、该值为14000 x (1/256kHz)~= 54.7us。 我们还怀疑数据表中可能有一个拼写错误;将 TD (RSSTA)的规格以 ns 为单位、而不是正确的 us。

期待着对这一问题作出一点澄清。

Don