主题中讨论的其他器件:LMK04828、、

您好!

具有 ADS54J66和 LMK04828的定制板。

ADC - fs = 311.93775 MHz、Sysref = 2.437011 MHz (FS/32*4)、K =32、LMFS = 4421、模式= 8旁路、 线路速率= 6.23875 Gbps (下面附加的 cfg 文件)

FPGA Xilinx ZCU102 - REFCLK = 311.9375 MHz、GlblClk = 155.96875 MHz

LMK - OSCIN 80.5MHz、VCO 0 = 2495.5MHz 时的参考时钟(在下面附加的 cfg 文件)

ADC 输入- 通道 A 为80.5MHz、通道 B、C 和 D 为100MHz。

我已在 ADS54J66EVM 上测试了相同的配置、但工作正常。

JESD 链路是稳定的、在实现同步时、CGS 和 ILA 级没有错误。

使用斜坡模式执行测试(见下文)。 输出看起来符合预期。 在此测试期间 、交错引擎0x680018 (写入0x03)和直流偏移校正0x680068 (写入0x06)被禁用。

使用自定义图形执行测试。 发送1从位0开始、然后将其移动一个位置到位1、位2、位3、依此类推、直到位13 (ADC 数据为14位)。

1) 1)测试图形00 0000 0001

2) 测试图形00 0000 0010

3) 测试模式00 0000 0100

4) 测试图形00 0000 1000

4) 测试图形00 0000 0001 0000

4) 测试图形00 0000 0010 0000

继续此测试、直到自定义图形10 0000 0000 0000

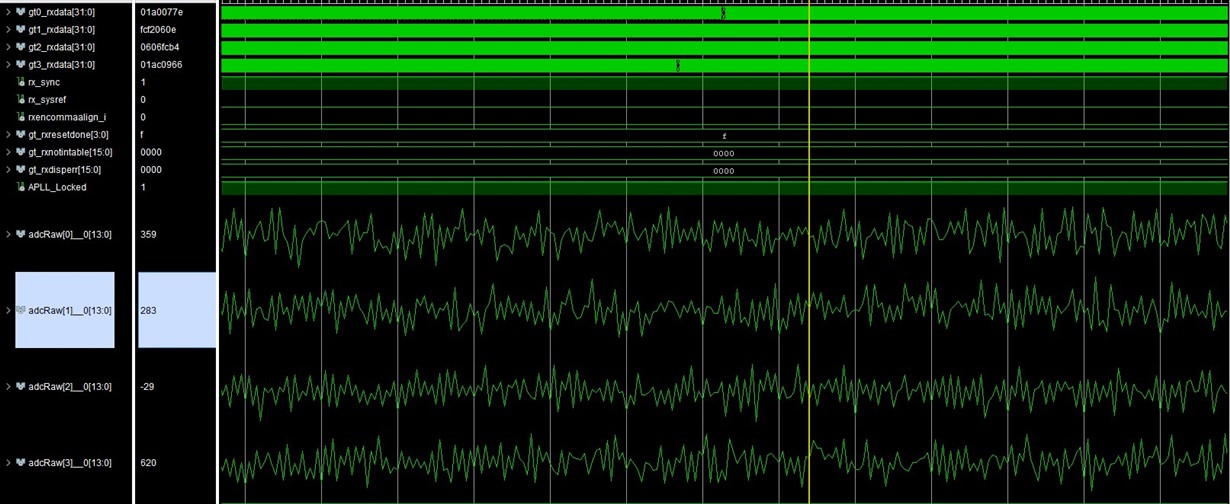

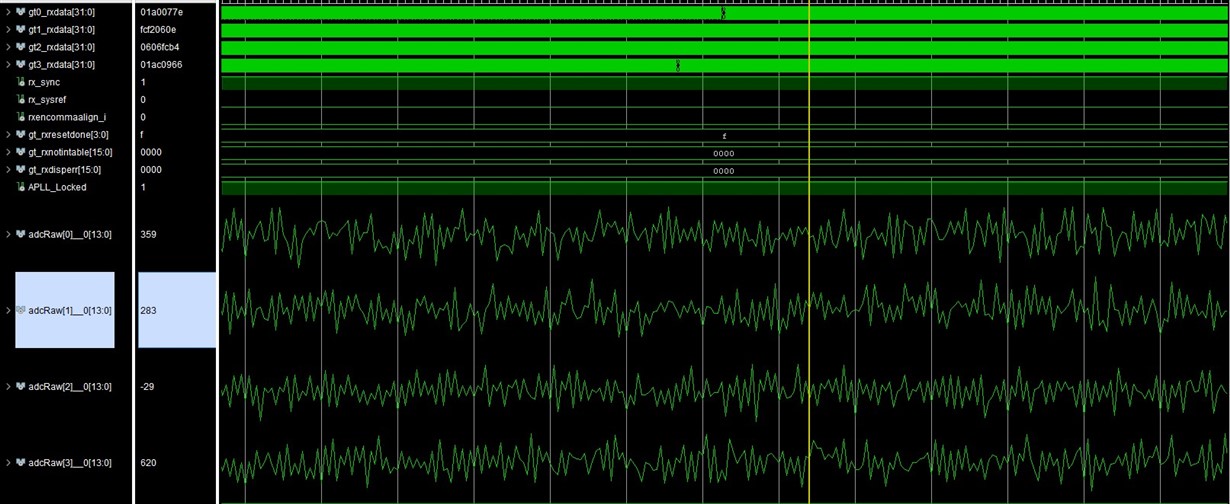

正常运行的 ADC 输出数据如下所示-

APLL_LOCK 信号表示 LMK04828上的 PLL2处于锁定状态。

我已经尝试将 ADC 输入的频率降低到1MHz、但输出看起来仍然一样。 原理图附在下面-

我探测了每个通道(C22、C15、C18和 C21)的频率、看起来不错。 请参见下面的附件(在 C22通道 A 上探测80.5 MHz)

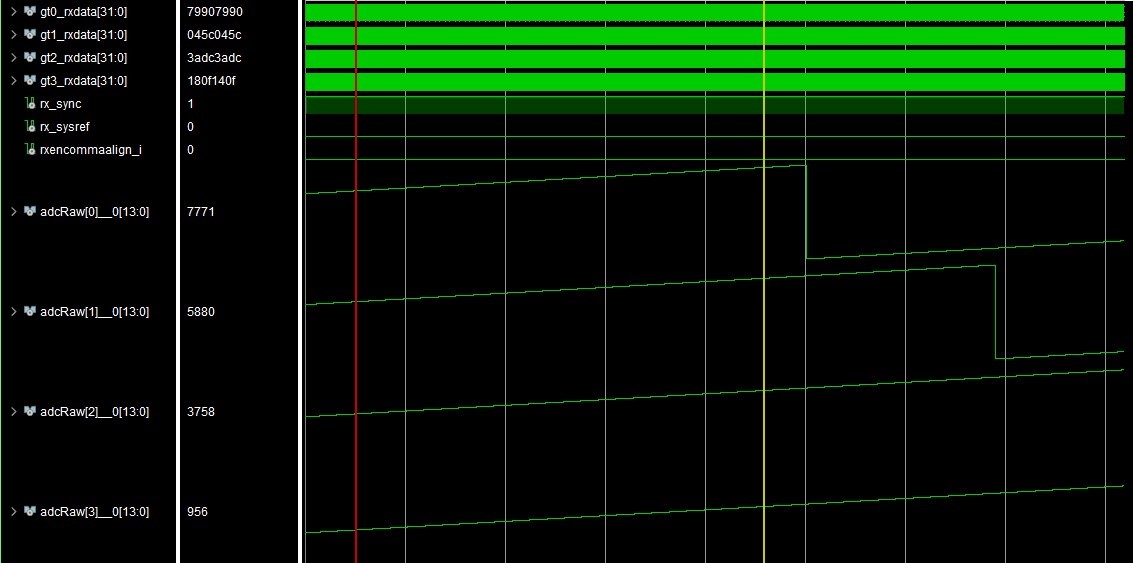

我已在 ADS54J66EVM 上测试了相同的配置、但工作正常。 我可以在 FPGA 上看到正弦波数据。 请参阅以下内容-

您能不能再为调试提供任何建议? 自定义原理图是否有任何问题?

e2e.ti.com/.../3056.ADS_5F00_4421_5F00_TI_5F00_Ticket_5F00_New.cfg

e2e.ti.com/.../LMK_5F00_ext80p5_5F00_311p9375MSPS_5F00_adc.cfg