数据表未指定 DRDY 相对于 SCLK 或 CLK 的时序参数。 DRDY 是否与任一时钟同步? DRDY 相对于 (哪个)时钟的最小/最大传播延迟是多少?

我想知道如何在所有条件下将 DRDY 安全地捕获到我的 ADC 接口中。 我应该在 CLK 或 SCLK 上注册 DRDY 吗? 还是应该将其视为异步和双寄存器?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

数据表未指定 DRDY 相对于 SCLK 或 CLK 的时序参数。 DRDY 是否与任一时钟同步? DRDY 相对于 (哪个)时钟的最小/最大传播延迟是多少?

我想知道如何在所有条件下将 DRDY 安全地捕获到我的 ADC 接口中。 我应该在 CLK 或 SCLK 上注册 DRDY 吗? 还是应该将其视为异步和双寄存器?

尊敬的 Aviva:

欢迎访问 TI E2E 论坛!

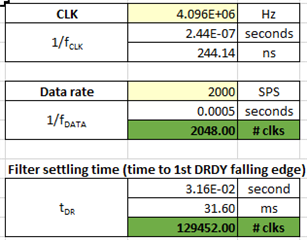

/DRDY 信号来自 CLK 信号;但是、遗憾 的是、我没有关于最小/最大传播延迟的任何信息。 假设该延迟 小于1个 CLK 周期、我预计/DRDY 下降沿将以以下速率出现:

您是否在对/DRDY 下降沿之间的时钟数进行计数、这是您尝试获得/DRDY 变为低电平时的准确计时的原因?

/DRDY 的主要用途是用作处理器的中断、以便其知道何时提取数据。 只要在下一个/DRDY 下降沿之前(即在下一个转换结果可用之前)读取数据、转换完成和读取数据的确切时间 通常不 是很严格。

此致、

Chris

Chris、您好、感谢您的回答。 不、我不会尝试对 DRDY 的时钟进行计数。 ( 无论如何、我从未成功计算过、因为我在非标准 fCLK = 3.571MHz 的正弦模式下运行)。 相反、我将 ADC 连接到 FPGA、并尝试确保在 DRDY 的捕获触发器处不会违反设置或保持时间。 当然、对于航天应用、我们会分析在所有条件下每个接口的检查情况。

我的应用程序目前在实验室中工作、没有特殊处理。 但在研究了这一点之后、 由于 TI 无法为此输出提供时序参数、我认为我的最佳做法是将 DRDY 视为异步并将其双寄存器写入 FPGA。 我有足够的时间读取数据、因此任何额外的几个时钟周期延迟对我来说都无关紧要。 这是一种非常保守的方法、但保证不会失败!